Hardware

Before I reinvent the wheel, here’s the quick intro from the manual, what an Inmos C004 actually is:

The IMS C004 is a transparent programmable link switch designed to provide a full crossbar switch between 32 link inputs and 32 link outputs. The IMS C004 will switch links running at either the standard speed of 10 Mbits/sec or at the higher speed of 20 Mbits/sec.

It introduces, on average, only a 1.75 bit time delay on the signal. Link switches can be cascaded to any depth without loss of signal integrity and can be used to construct reconfigurable networks of arbitrary size. The switch is programmed via a separate serial link called the configuration link.

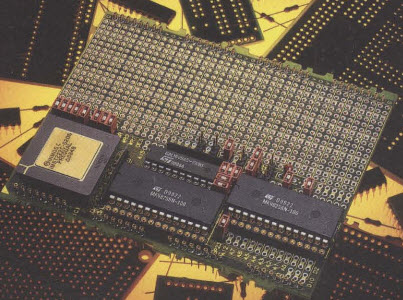

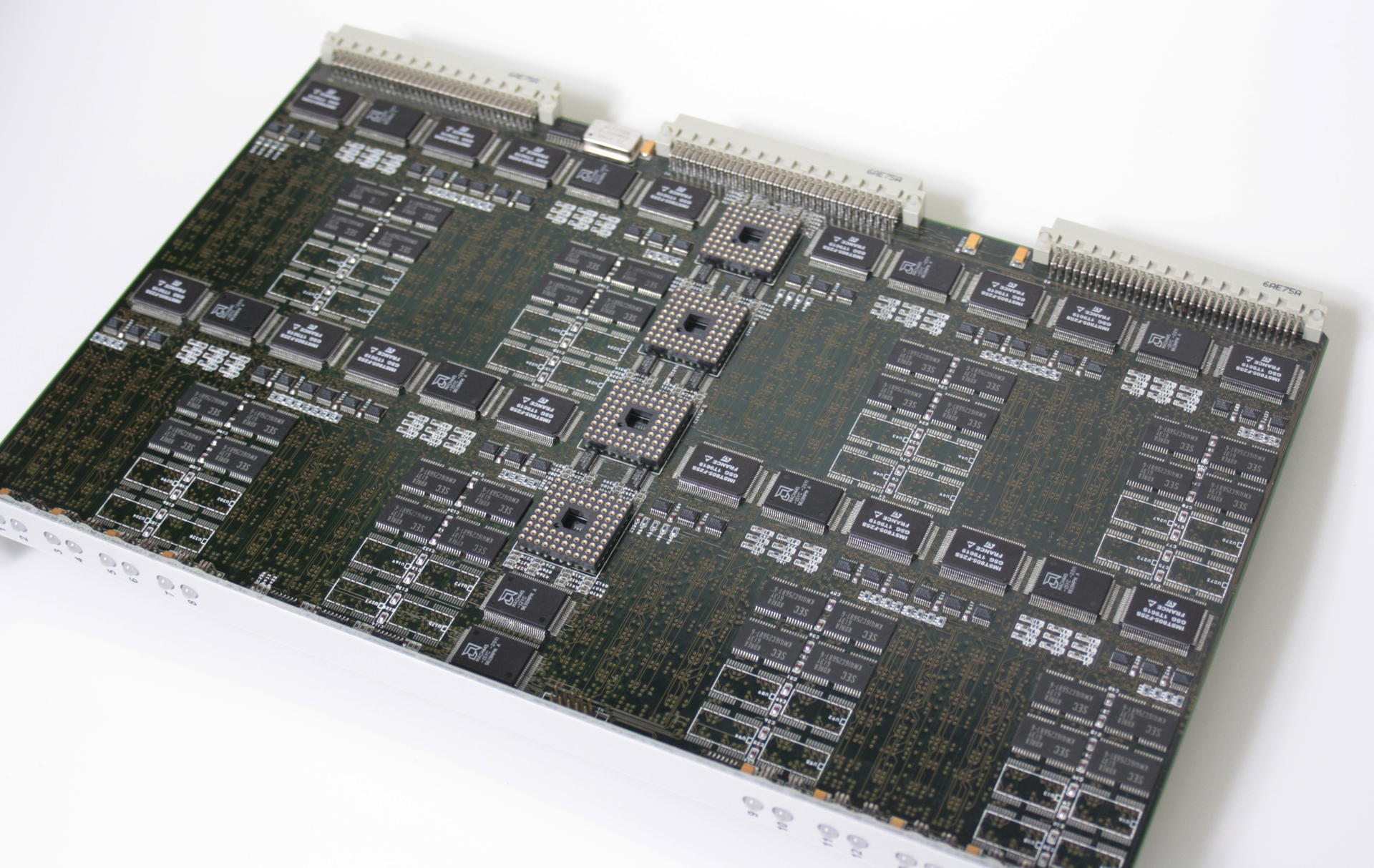

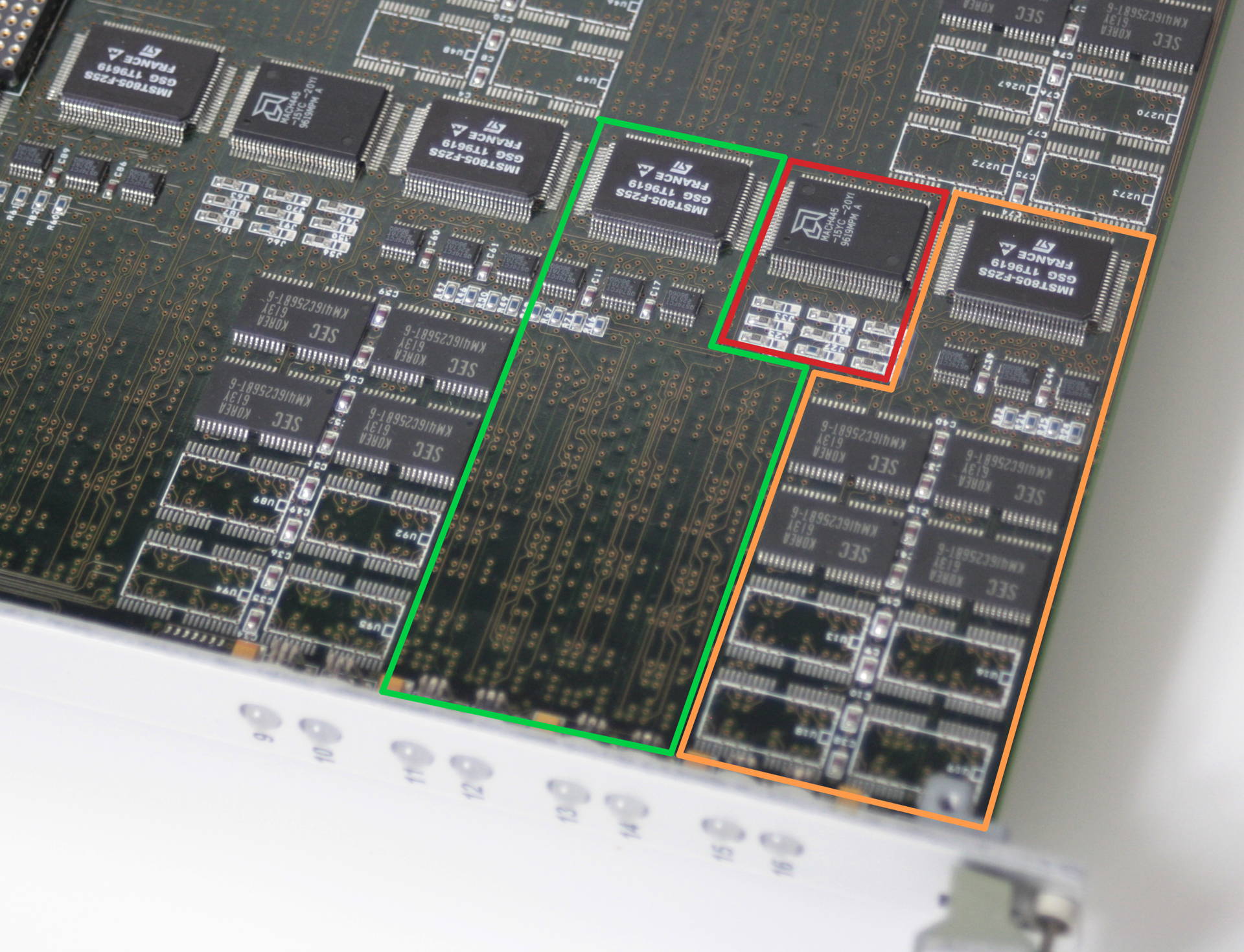

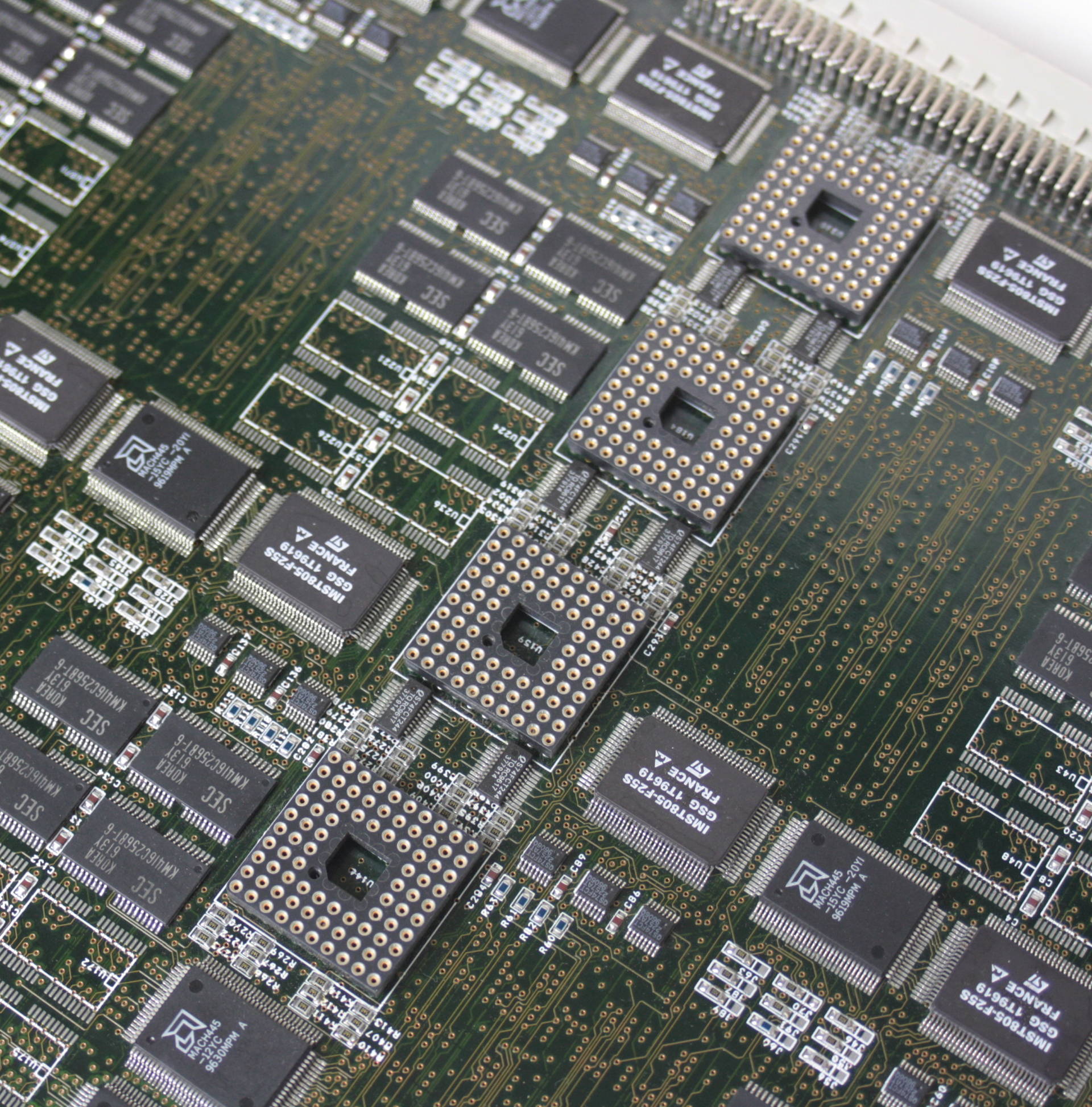

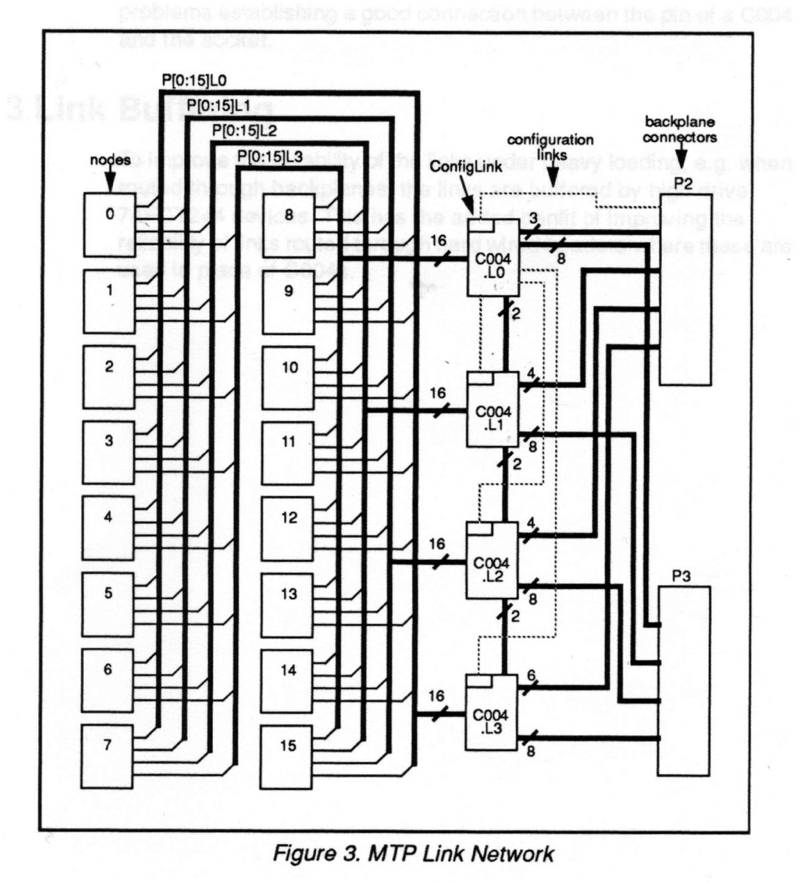

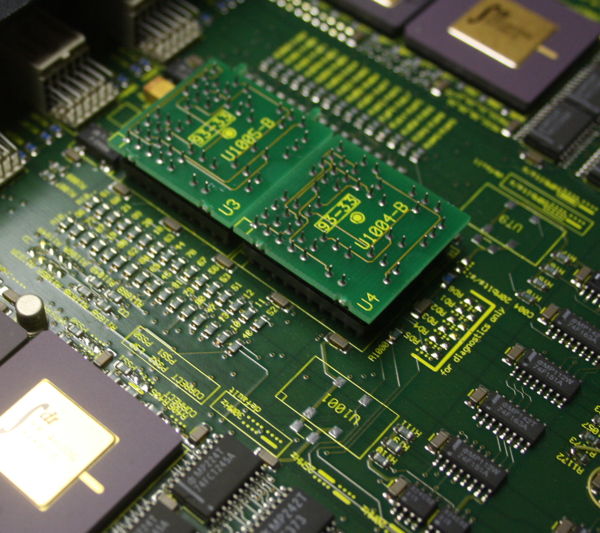

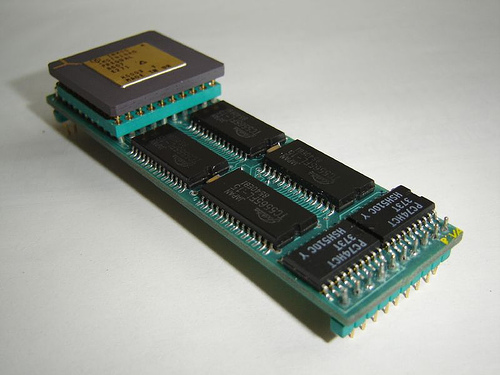

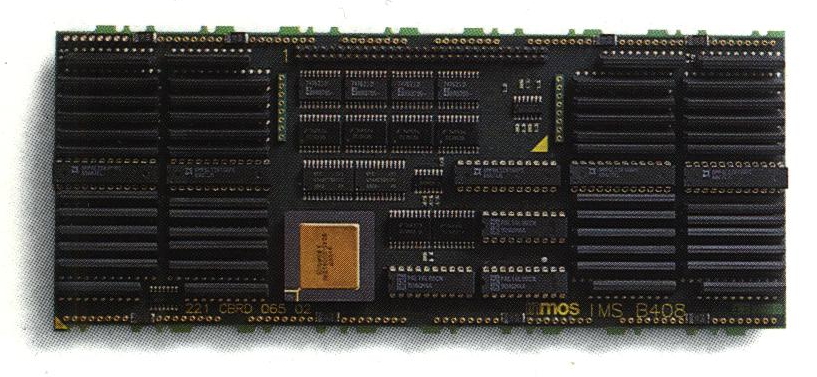

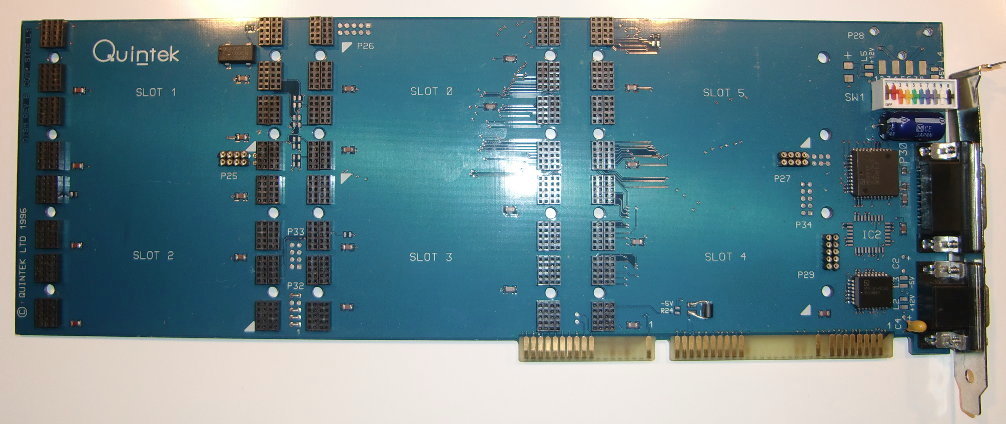

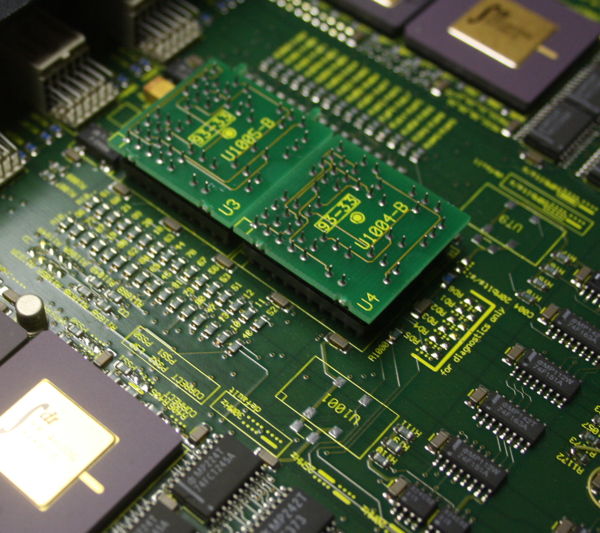

So in simple words: 32 inputs can be freely connected to 32 outputs. Great for large Transputer networks which can be reconfigured only by reprogramming the C004 – on top of that, you can cascade them and create huge, complex networks to make any connection imaginable possible. Like those Parsytec used in their SuperCluster machines looking like this:

Yes, that’s 13 C004s and one Transputer to rule them all…

Yes, that’s 13 C004s and one Transputer to rule them all…

… so much for the theory.

In practice, the C004 is a bitch. Not only does it require a Transputer to configure it (normally a 16bit T2xx) it also adds quite a delay into the link-communication. As mentioned above, it’s “only a 1.75 bit time delay” but this can sum up to quite an amount.

Let me quote some more realistic numbers from the Helios manual (pp.255):

It is of interest to ascertain the effect of the Inmos C004 on the performance of the Helios communication mechanisms. Figure 6.3 illustrates the rates of data communication (Kbytes/second) attained using message passing primitives (PutMsg() and GetMsg()) between two Transputers that were

1. Directly linked and

2. Connected through a C004 link switch.

It is evident from Figure 6.3 that the effect of the C004 link switch on the rate of communication is far from negligible. The overhead imposed by the link switch increases with the size of the message. In the worst case (64 Kbyte message), transmission through the C004 is 23 % slower than sending data over directly connected links.

Oops. 23% is quite essential. So before planning to set up a crazy C004 network you might consider what you want to achieve.

Is it for educational network studies only? Fine.

Are you going for speed and rarely change your Transputer network configuration? Avoid it!

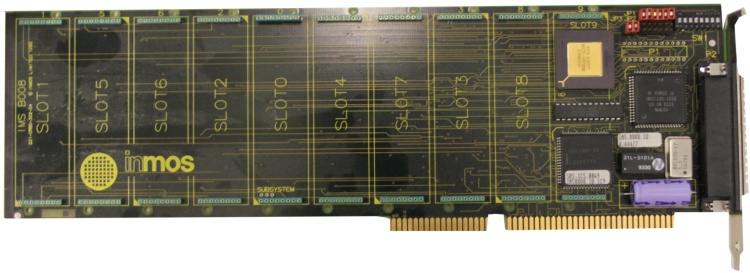

IMHO even the 10 possible Transputers on an IMSB008 do not require a C004 making your day.

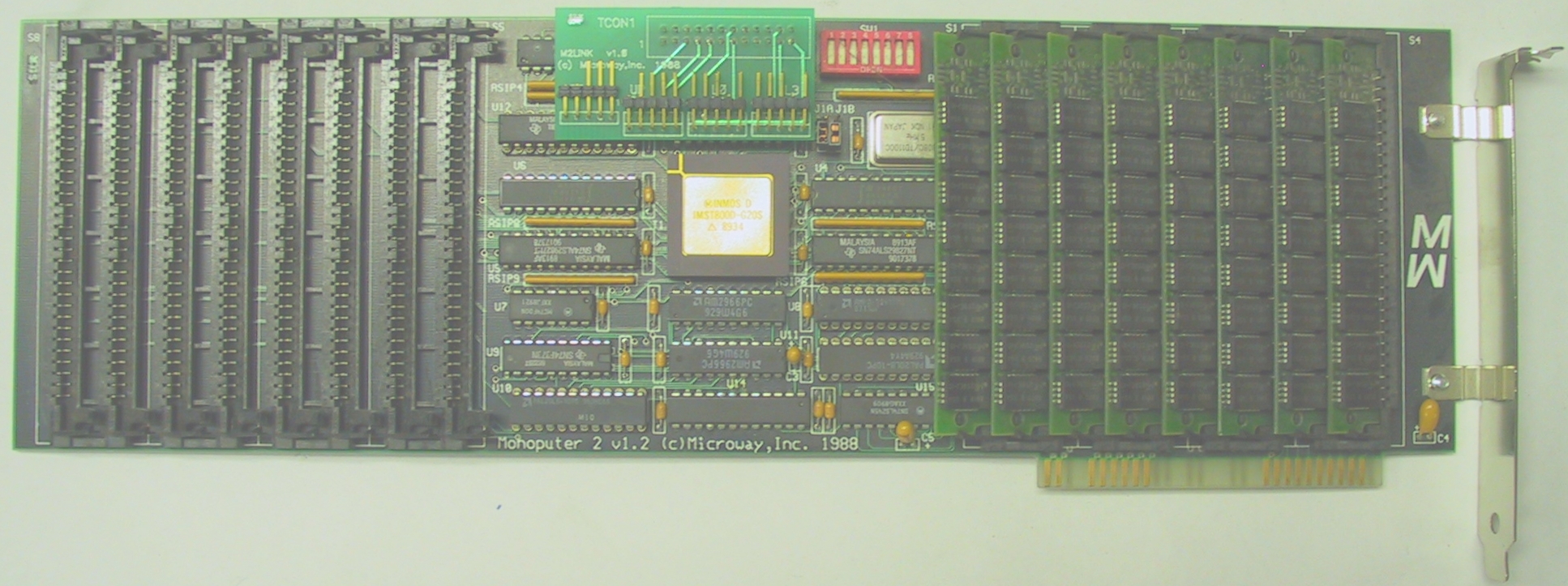

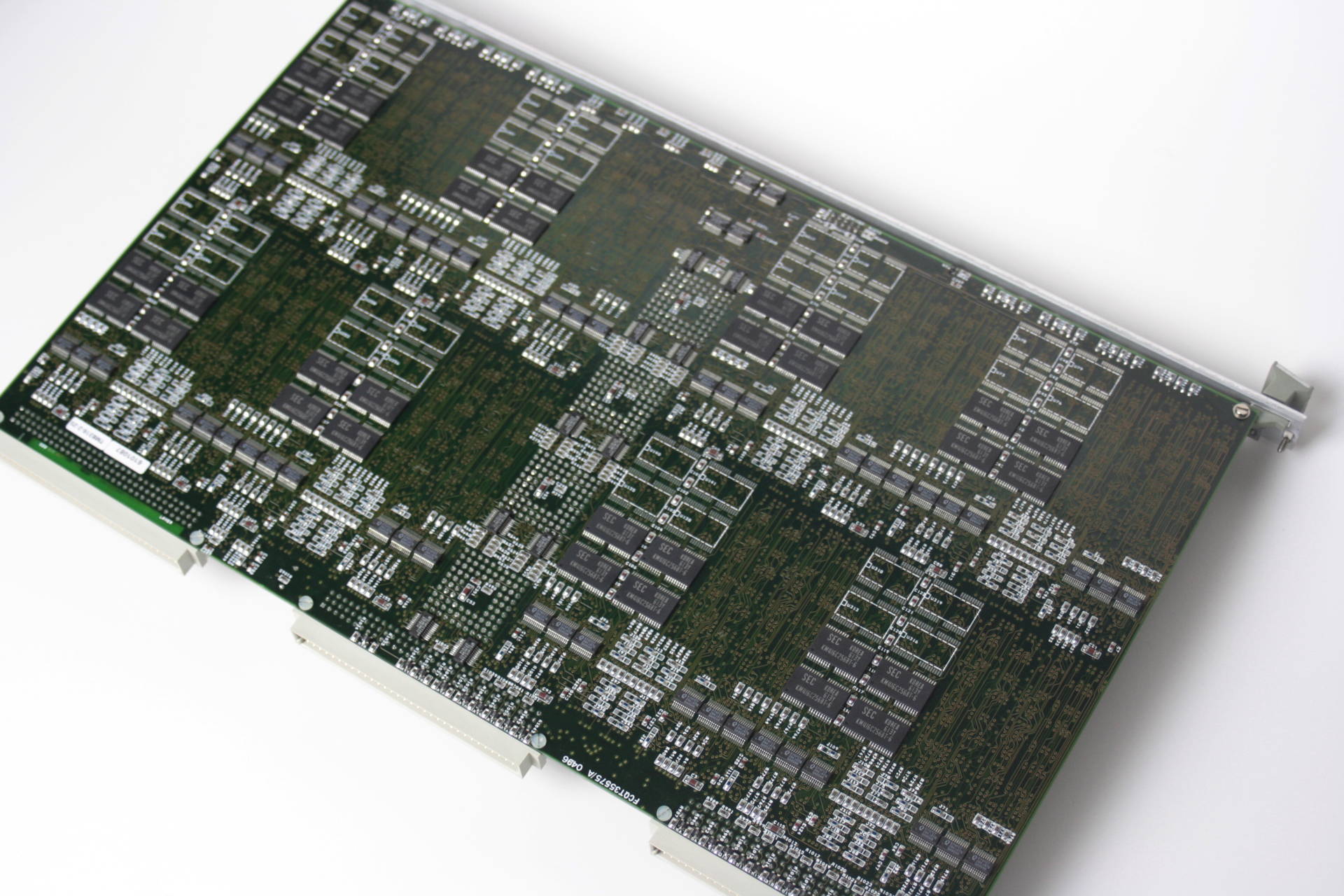

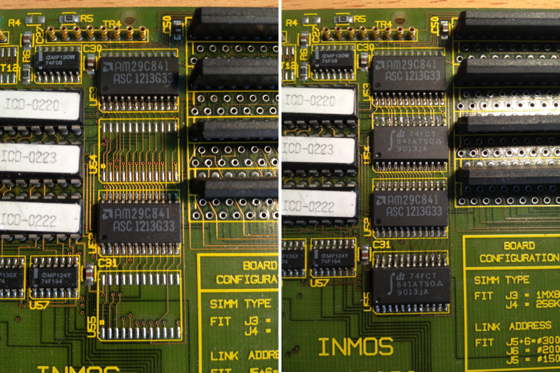

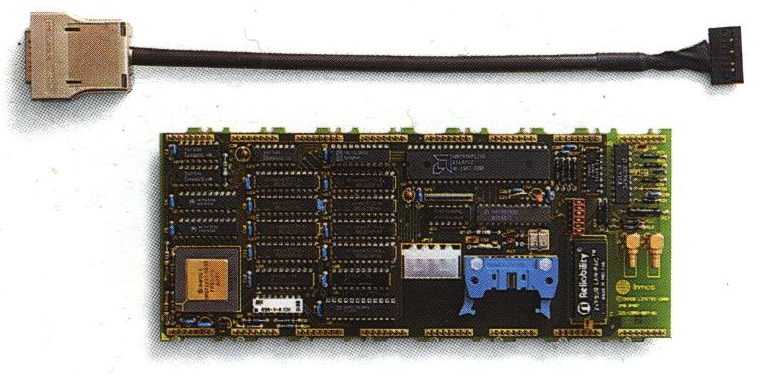

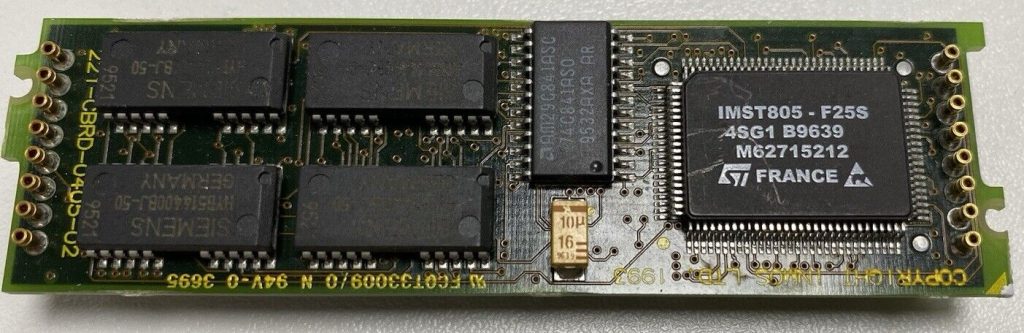

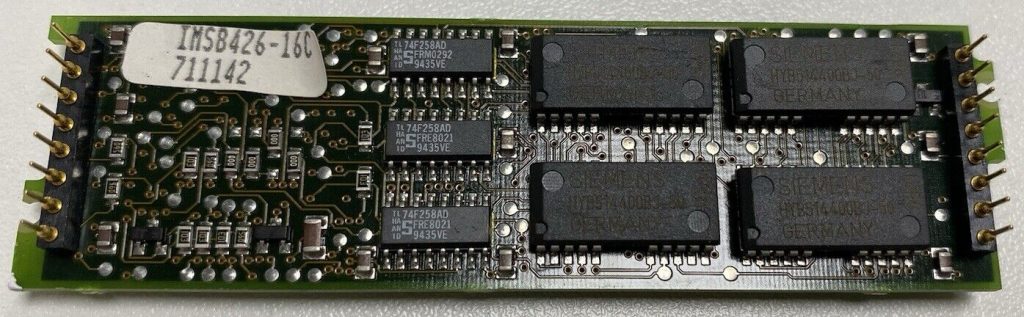

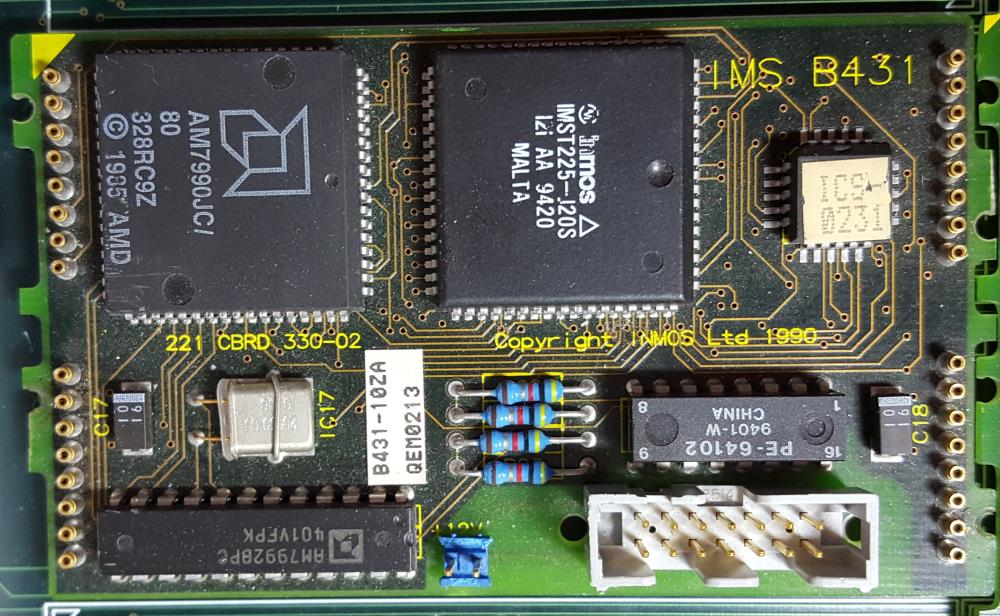

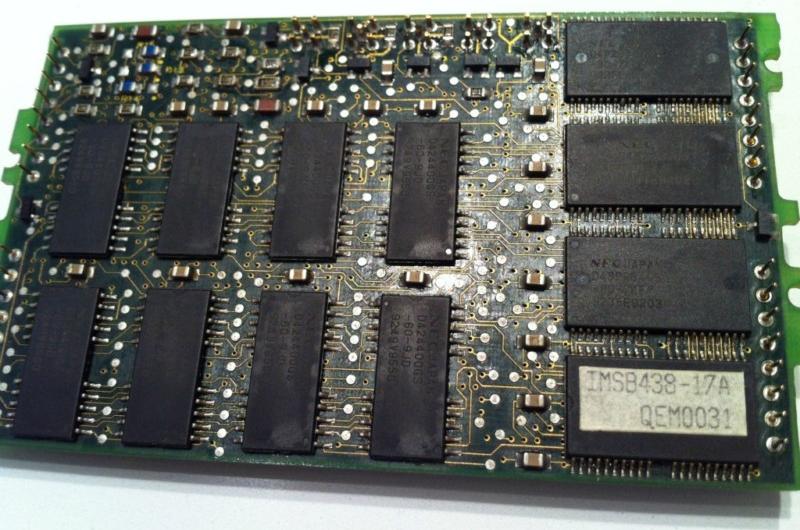

Actually, even Parsytec thought that this is useless to use a link switch for the 16 Transputers in their beautiful x’plorer and replaced it by hard-wire dummies:

Configuration

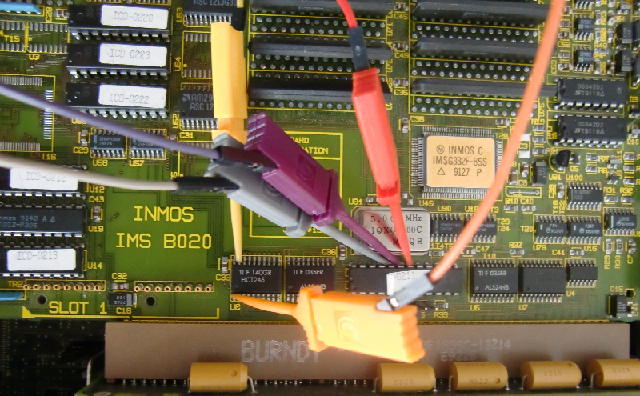

Ok, you’re still not scared away and really do like to know how to handle that beast. Fine, here’s what I went through:

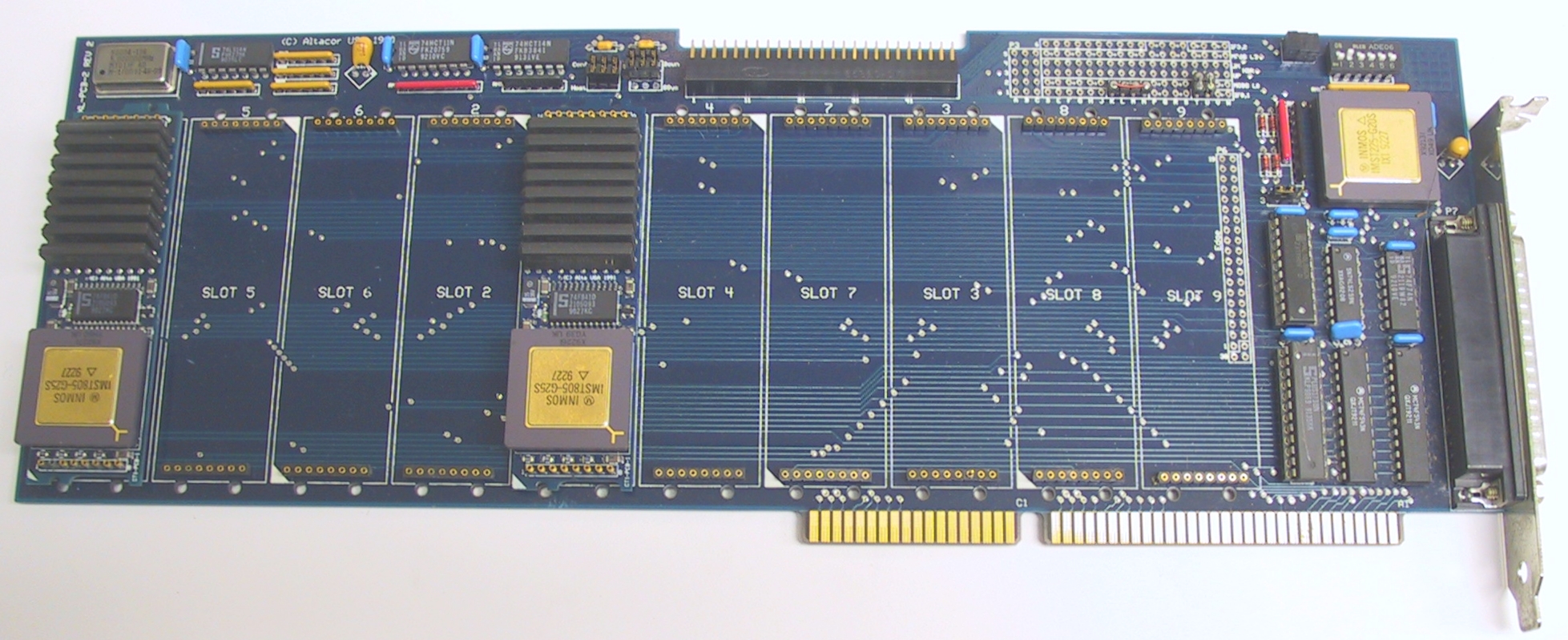

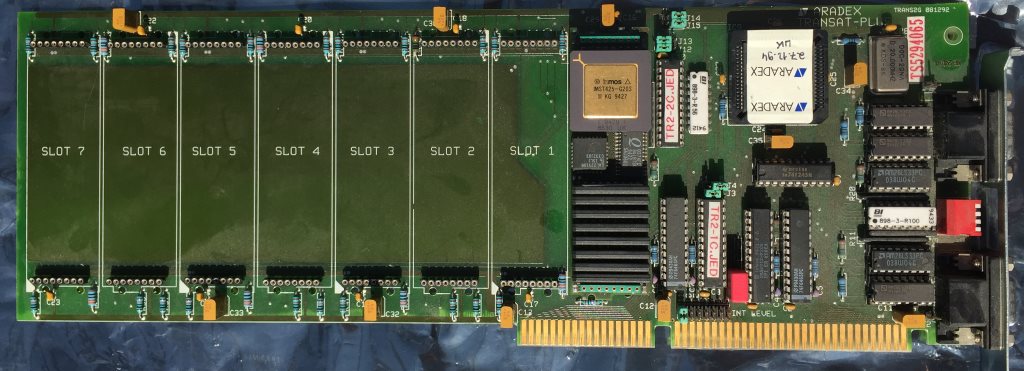

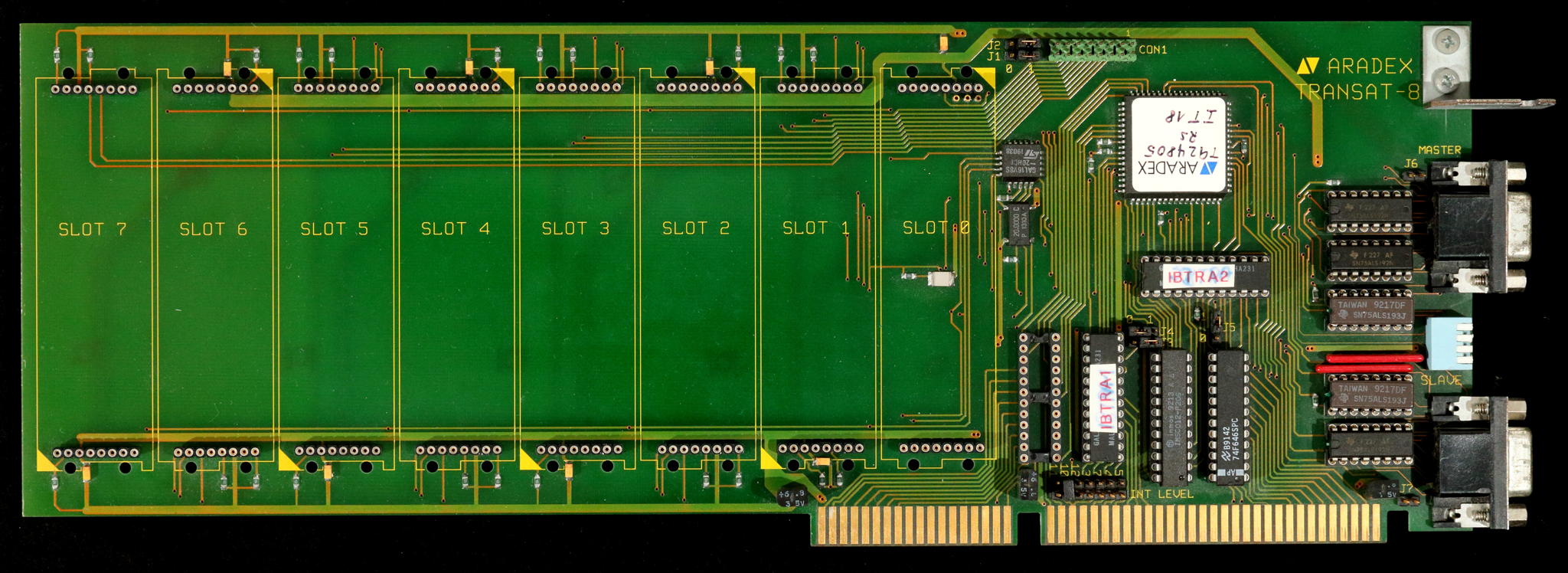

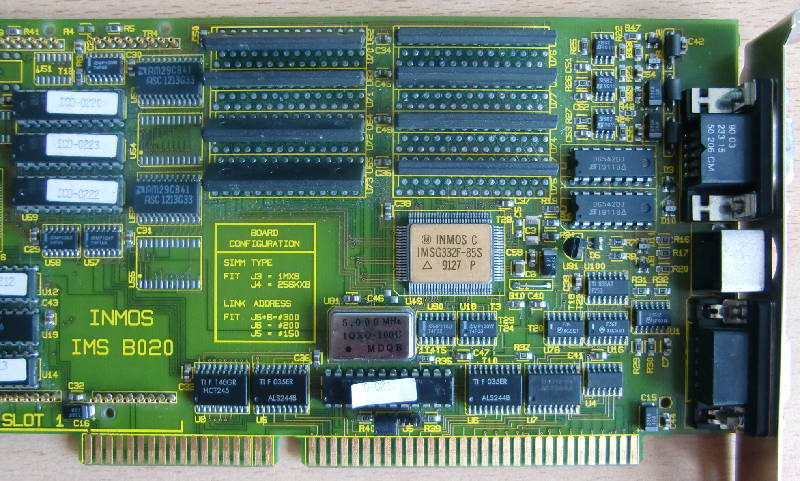

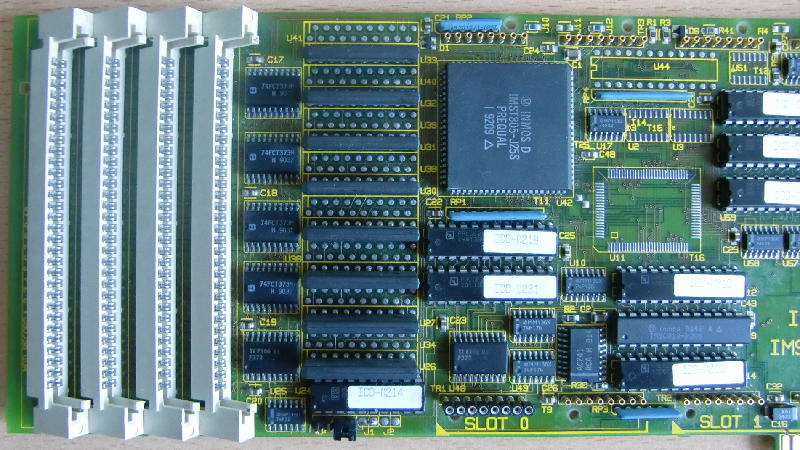

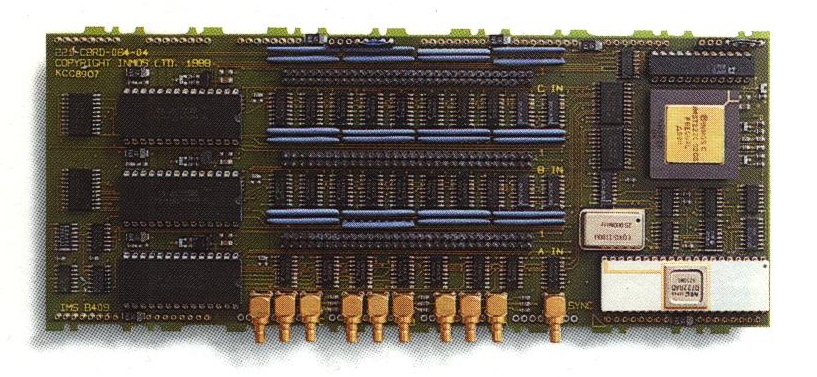

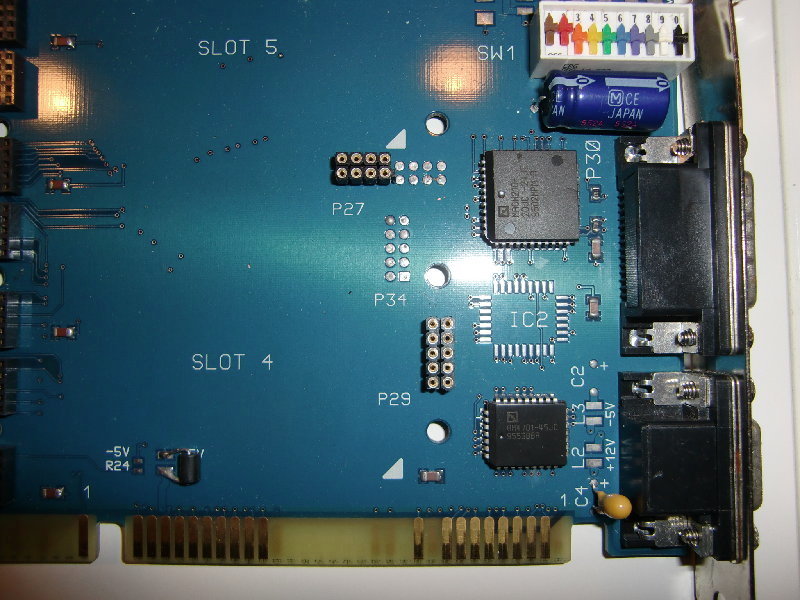

To work with a C004 you obviously need either a TRAM carrier like the B008 or some sort of motherboard like the IMSB012 or IMSB014. Read the boards manual to understand how to connect to the T2xx Network Control Processor (NCP).

For example the IMSB012 has extra pins for “config down” (i.e. IN) and “config up” (i.e. OUT) for its T212 and any other boards being chained to it.

As for the IMSB008 has its T222 connected to Link 1 of TRAM 0.

The hardware wiring is important to know, because this information is needed for the so-called hardwire file used by the INMOS tool “MMS2” (Module Motherboard Software, MSDOS only, the manual is available here).

After reading the manual (do!) you should be able to read this hardwire file for an B008 quite easily. It describes the complete hardware setup and all physical connection between the C004(s), T2xx and Transputer/TRAM links on the board:

-- B008 hardwire description

DEF B008

SIZES

T2 1

C4 1

SLOT 10

EDGE 10

END

T2CHAIN

T2 0, LINK 3 C4 0

END

HARDWIRE

SLOT 0,LINK 2 TO SLOT 1,LINK 1

SLOT 1,LINK 2 TO SLOT 2,LINK 1

SLOT 2,LINK 2 TO SLOT 3,LINK 1

SLOT 3,LINK 2 TO SLOT 4,LINK 1

SLOT 4,LINK 2 TO SLOT 5,LINK 1

SLOT 5,LINK 2 TO SLOT 6,LINK 1

SLOT 6,LINK 2 TO SLOT 7,LINK 1

SLOT 7,LINK 2 TO SLOT 8,LINK 1

SLOT 8,LINK 2 TO SLOT 9,LINK 1

C4 0,LINK 10 TO SLOT 0,LINK 3

C4 0,LINK 1 TO SLOT 1,LINK 0

C4 0,LINK 11 TO SLOT 1,LINK 3

C4 0,LINK 2 TO SLOT 2,LINK 0

C4 0,LINK 12 TO SLOT 2,LINK 3

C4 0,LINK 3 TO SLOT 3,LINK 0

C4 0,LINK 13 TO SLOT 3,LINK 3

C4 0,LINK 4 TO SLOT 4,LINK 0

C4 0,LINK 14 TO SLOT 4,LINK 3

C4 0,LINK 5 TO SLOT 5,LINK 0

C4 0,LINK 15 TO SLOT 5,LINK 3

C4 0,LINK 6 TO SLOT 6,LINK 0

C4 0,LINK 16 TO SLOT 6,LINK 3

C4 0,LINK 7 TO SLOT 7,LINK 0

C4 0,LINK 17 TO SLOT 7,LINK 3

C4 0,LINK 8 TO SLOT 8,LINK 0

C4 0,LINK 18 TO SLOT 8,LINK 3

C4 0,LINK 9 TO SLOT 9,LINK 0

C4 0,LINK 19 TO SLOT 9,LINK 3

C4 0,LINK 20 TO EDGE 0

C4 0,LINK 21 TO EDGE 1

C4 0,LINK 22 TO EDGE 2

C4 0,LINK 23 TO EDGE 3

C4 0,LINK 24 TO EDGE 4

C4 0,LINK 25 TO EDGE 5

C4 0,LINK 26 TO EDGE 6

C4 0,LINK 27 TO EDGE 7

-- Uncomment the next two lines if the

-- patch header wiring is used to

-- connect C004, link 28 to PatchLink0,

-- and C004, link 29 to PatchLink1.

-- C4 0,LINK 28 TO EDGE 8

-- C4 0,LINK 29 TO EDGE 9

END

PIPE B008 END

After that’s done, you can prepare a second file. The so called “softwire file” which actually tells the T2xx how to internally connect his in- and out-links. A very simple example would be:

SOFTWIRE

PIPE 0

SLOT 0,3 TO SLOT 1,3

END

This would connect TRAM-0’s 3rd link to TRAM-1’s 3rd link.

Now that you have the necessary config files let’s move on to the MMS itself.

Software

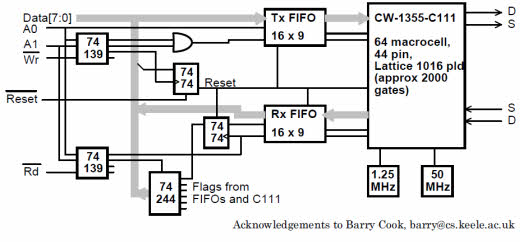

As with nearly every software from INMOS the MMS too is written in OCCAM and therefore has to run on a Transputer. This might be the one in TRAM slot 0 on your B008 or on a local ISA board which itself is connected with 2 links to a B012 (one for config and one to the Transputer network).

To make things easier, I prepared a complete MMS archive to download here (links to my Transputer Software page).

It contains some example soft- and hardwire files, an ISERVER.EXE (the program you need to upload code into your Transputer) as well as a batch file to easily start MMS (RUN_MMS.BAT).

Also you will find a folder with INMOS’ pimped version of ANSI.SYS called BANSI (“Better ANSI”), because all INMOS tools make heavy use of ANSI screen control. So put that into your CONFIG.SYS.

Before we begin, let’s have a look at my IMSB012 with ispy:

ispy 2.33

# Part rate Mb Bt [ Link0 Link1 Link2 Link3 ]

0 T800d-25 0.37 0 [ HOST 1:1 2:1 ... ]

1 T2 -20 1.64 1 [ ... 0:1 ... ... ]

2 T800d-25 1.75 1 [ ... 0:2 3:1 ... ]

3 T800d-25 1.77 1 [ ... 2:2 4:1 ... ]

4 T800d-25 1.77 1 [ ... 3:2 5:1 ... ]

5 T800d-25 1.75 1 [ ... 4:2 6:1 ... ]

6 T800d-25 1.75 1 [ ... 5:2 7:1 ... ]

7 T800d-25 1.75 1 [ ... 6:2 8:1 ... ]

8 T800d-25 1.75 1 [ ... 7:2 9:1 ... ]

9 T800d-25 1.75 1 [ ... 8:2 10:1 ... ]

10 T800d-25 1.75 1 [ ... 9:2 11:1 ... ]

11 T800d-25 1.75 1 [ ... 10:2 12:1 ... ]

12 T800d-25 1.75 1 [ ... 11:2 13:1 ... ]

13 T800d-25 1.77 1 [ ... 12:2 14:1 ... ]

14 T800d-25 1.77 1 [ ... 13:2 15:1 ... ]

15 T800d-25 1.75 1 [ ... 14:2 16:1 ... ]

16 T800d-25 1.77 1 [ ... 15:2 17:1 ... ]

17 T800d-25 1.77 1 [ ... 16:2 ... ... ]

Ok, let’s start MMS2. Use/modify the batch “run_mms.bat” which will do all environment variables expected by iserver.exe and also adds the input and output files – change it as you please.

If everything works fine, iserver loads MMS2.B4 onto your Transputer and executes it. Your screen should look like the screenshot below.

First, I suggest you press “c” for checking the consistency of your hard/softwire files – if everything’s fine, MMS2 will print “Source files checked O.K.” as seen in the lowest line in the screenshot.

Just for the fun of it, you can try MMS’ very own network worm – so press “n” to start the network mapper. You will see that it is much slower than e.g. ispy, so just be patient.

After some seconds, you should get something like this:

Now it’s time to program you network. So press “s” to set the C004(s). Some infos will rush trough the bottom line of the screen and finally MMS2 states “C004 setting preformed O.K.“:

Nothing more to do here so press “q” to quit MMS2. (Do not run the network mapper again! It seems to reset the T2 and in my case reproducibly crashes the network).

It’s better to use ispy. ispy v2.33 to be precise. I encountered several issues with the C004 and the most recent version 3.23 of ispy.

So running ispy including the /C4 switch to display the settings of the two C004s now shows this – mind all the new connections of each Transputers Link0 and 3:

ispy 2.33

# Part rate Mb Bt [ Link0 Link1 Link2 Link3 ]

0 T800d-25 0.37 0 [ HOST 1:1 4:1 ... ]

1 T2 -20 1.74 1 [ 2:C 0:1 ... 3:C ]

2 C004b [ 6S3JM54V --U8-1C- -G--F9-I T--7-PQ- ]

3 C004b [ -D-2650R BL--E--K H-N3--4- -TU-1OA7 ]

4 T800d-25 1.65 1 [ ... 0:2 5:1 6:0 ]

5 T800d-25 1.75 1 [ ... 4:2 7:1 8:0 ]

6 T800d-25 1.41 0 [ 4:3 9:2 8:1 10:0 ]

7 T800d-25 1.75 1 [ ... 5:2 9:1 11:0 ]

8 T800d-25 1.41 0 [ 5:3 6:2 11:1 12:0 ]

9 T800d-25 1.75 2 [ ... 7:2 6:1 13:0 ]

10 T800d-25 1.35 0 [ 6:3 13:2 12:1 14:0 ]

11 T800d-25 1.41 0 [ 7:3 8:2 13:1 15:0 ]

12 T800d-25 1.42 0 [ 8:3 10:2 15:1 16:0 ]

13 T800d-25 1.32 0 [ 9:3 11:2 10:1 17:0 ]

14 T800d-25 1.35 0 [ 10:3 17:2 16:1 ... ]

15 T800d-25 1.41 0 [ 11:3 12:2 17:1 18:0 ]

16 T800d-25 1.33 0 [ 12:3 14:2 18:1 ... ]

17 T800d-25 1.32 0 [ 13:3 15:2 14:1 19:0 ]

18 T800d-25 1.35 0 [ 15:3 16:2 19:1 ... ]

19 T800d-25 1.32 0 [ 17:3 18:2 ... ... ]

Yay! It worked. Positively as well as negatively.

Besides the new connections you might also spot a difference in the link-speed column. In our first run of ispy all Transputers had a link-speed around 1.75MBps. Now it varies between 1.75 and 1.32, depending on how often the ispy worm crossed a C004.

Two final hints:

If your C004 network has been set-up as planned, you can use ispys output to programm the network later.

Just save the output into an ASCII file (ispy /c4 > my_net.txt) and when needed feed it back into ispy like this:

ispy /r /cr < my_net.txt

This will reset the network and read in the configuration from stdin.

Obviously you can also manually edit the text file, the c4 lines

2 C004b [ 6S3JM54V --U8-1C- -G--F9-I T--7-PQ- ]

3 C004b [ -D-2650R BL--E--K H-N3--4- -TU-1OA7 ]

which isn’t as comfortable and comprehensible as editing a hard/softwire file. But your mileage my vary.

Alternatively, MMS2 can create a bootable file with your network settings. This can be used for quickly setting-up your system.

Just hit the “b” key and enter a filename. My MMS2 archive contains the above example as “BOOTB012.BTL”. Run it with “iserver /SB bootb012.btl“.

Caveats

Mind your reset! This means, in many cases a root Transputer might reset all the “worker Transputers” but also your T2xx and in effect all C004. So be careful when resetting your system.

Yes, theoretically you can reconfigure your Inmos C004 on the fly while all connected Transputer run. The most prominent example is having one network topology during data acquisition while changing it for number crunching later on.

This requires a very good knowledge of the notwork and thorough process locking etc.