INMOS was obviously the first manufacturer of TRAMs. Over the time you can clearly see the progress the technology made over the period Inmos TRAMs were made. Starting with comparably big sizes, using DIP chips etc. the last of its breed were highly integrated PCBs cramped with SMD parts and chips.

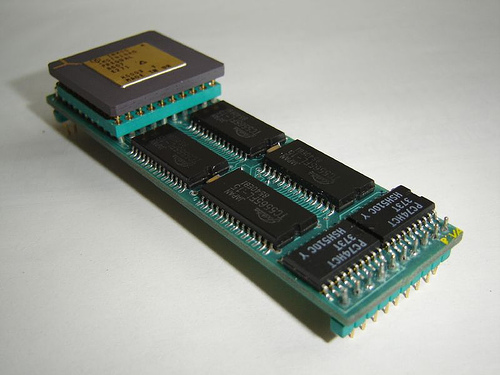

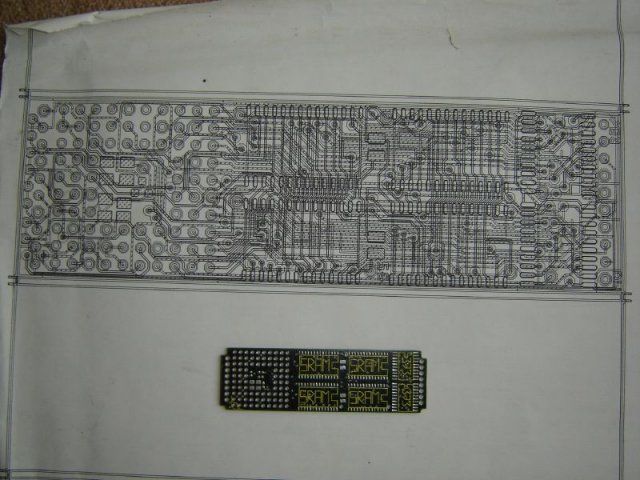

The IMS B401 started it all. A 32KB SRAM size-1 TRAM for a 32-bit Transputer. Here’s the prototype, the final product and a picture of its schematic:

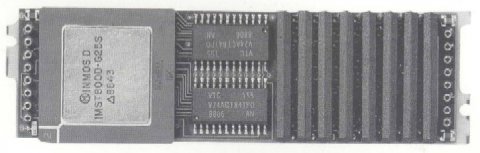

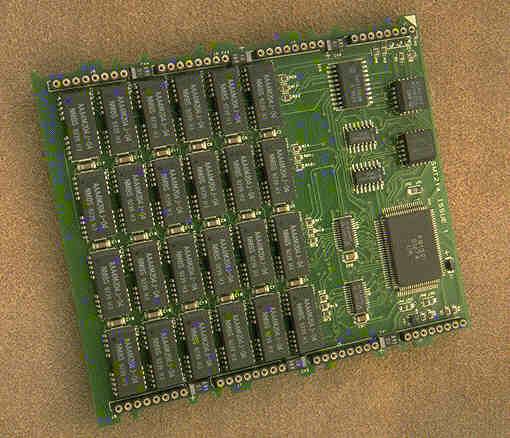

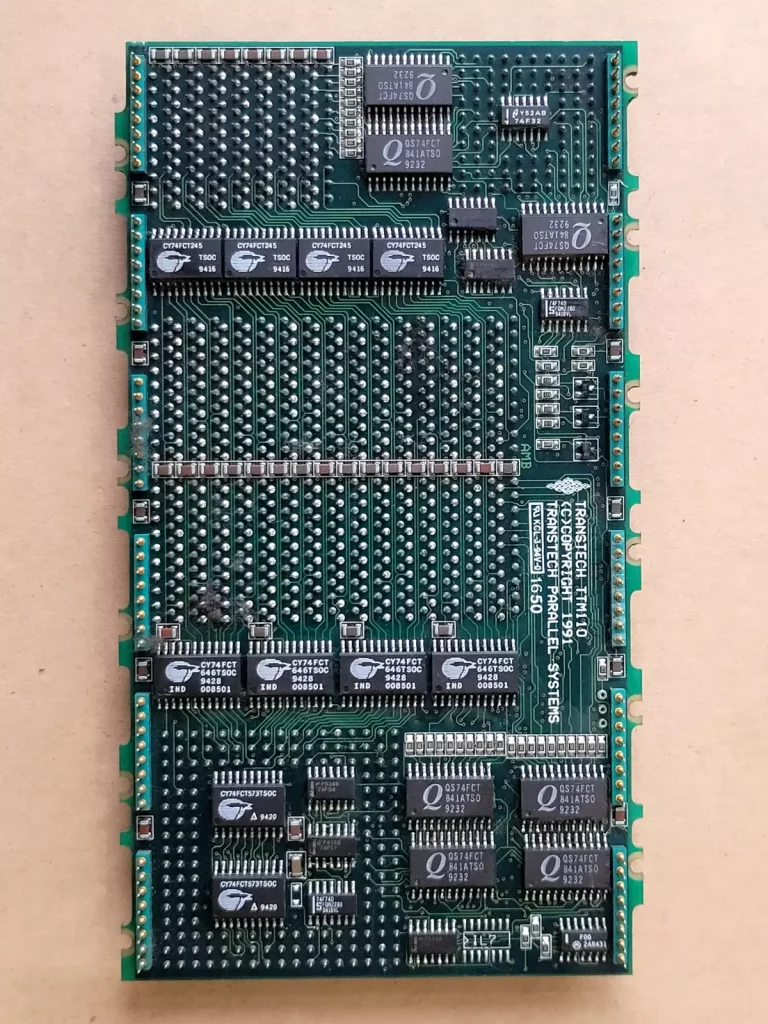

The “huge” IMS B403 1Mbyte DRAM Size-4 TRAM:

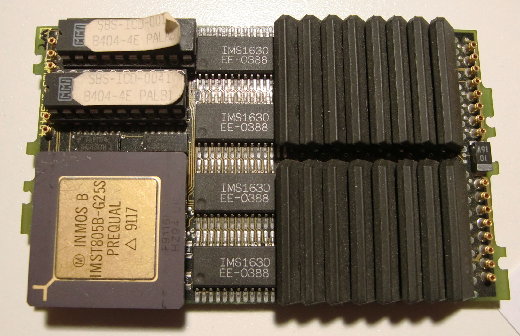

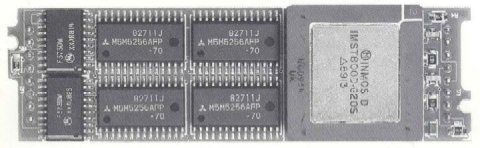

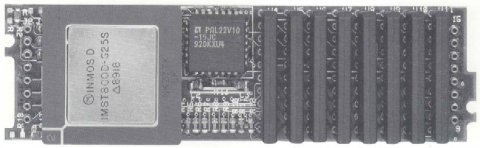

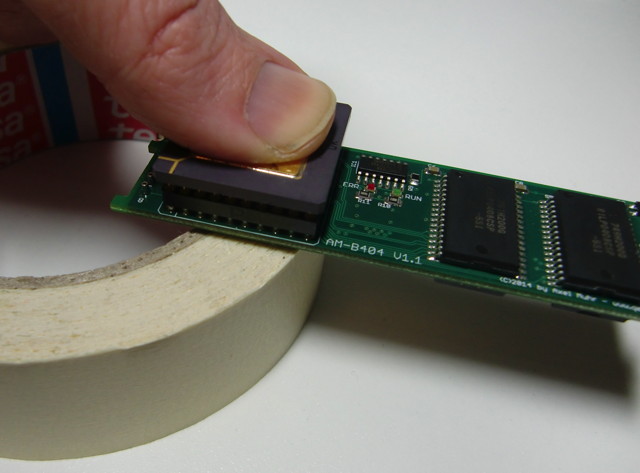

The IMS B404 (2MB DRAM, Size-2) is where the fun starts. Size-2 is just OK not to totally hog your mainboard and 2MB is what you need for OCCAM or HELIOS to make something useful.

Actually, the B404 has 3 “levels” of RAM. 4K internally in the Transputer, 32K SRAM and 2048K DRAM. As they are superimposed (i.e. overlapping), the total amount is still 2MB with different access speed at 0-4k (1 cycle), 5-32k (3 cycles) and 4-5 cycles above.

There were also the IMSB402 (8Kbyte Size-1) and the IMSB405 8Mbyte Size-8 TRAMs of which I have no pictures yet.

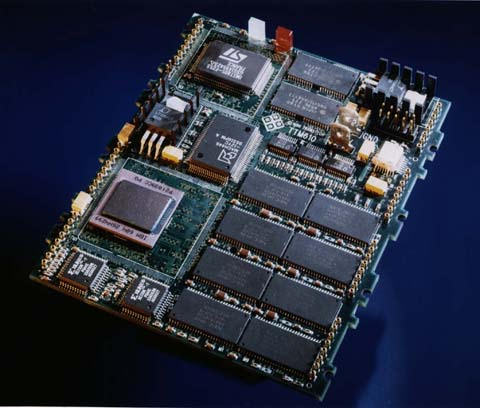

The IMS B407 was an Ethernet TRAM (Size-8!), proving that a TRAM doesn’t need to be necessarily a Transputer Module for number crunching only.

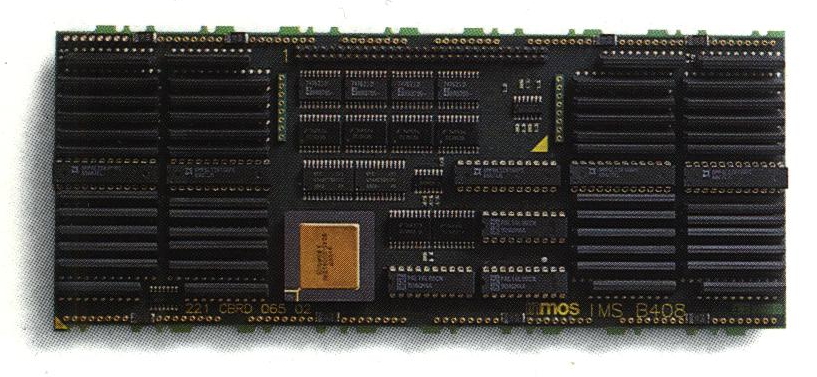

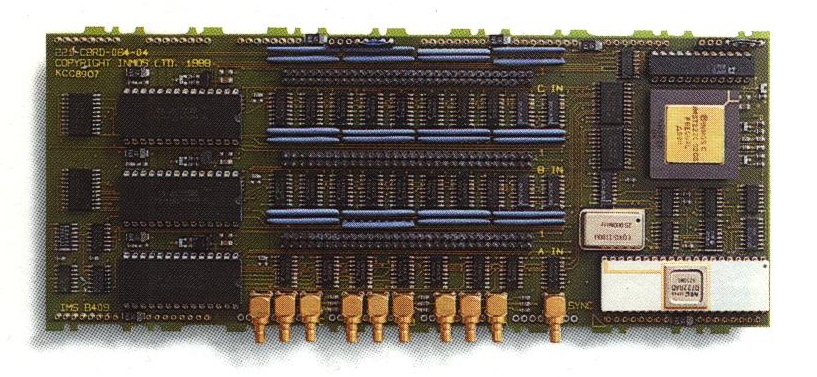

The IMS B408 and B409 were both part of a graphics system, so you didn’t the to have the host to render the graphics – which would have been much slower than those TRAMs.

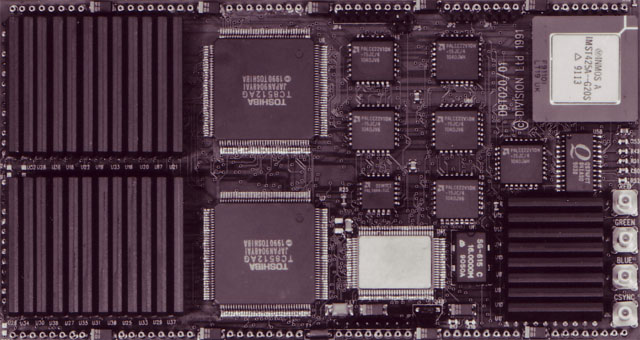

The B408 was the “drawing pad image storage” (1,25MB dual-ported RAM), while the B409 had the timing generator and the CLUTs:

The IMS B411 can be seen as a new era: 1MB DRAM on just a size-1 TRAM made possible by the use of small ZIP-packaged DRAMs… which were very expensive, of course.

The IMS B415 is a simple Transputer-Link to RS422 converter. This way, link connections can span up to 30 meters.

The IMS B416 features a 16bit T2xx Transputer and 64KB SRAM

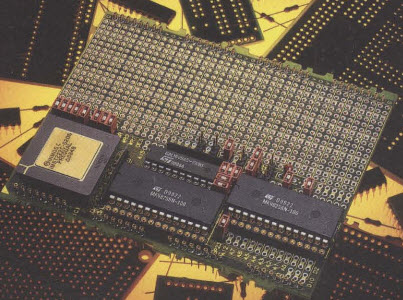

The IMS B417 is a massive beast: 4MB on a size-4 TRAM… well, still better than the B403.

The IMS B418 contains a 16-bit T222 and 256KB Flash ROM… quite modern stuff those days and probably a good way to boot your HELIOS system from 😉

The IMS B419 combined the two huge B408 and B409 modules into one size-6 TRAM. A nice graphics TRAM with 2MB DRAM and 2MB VRAM…

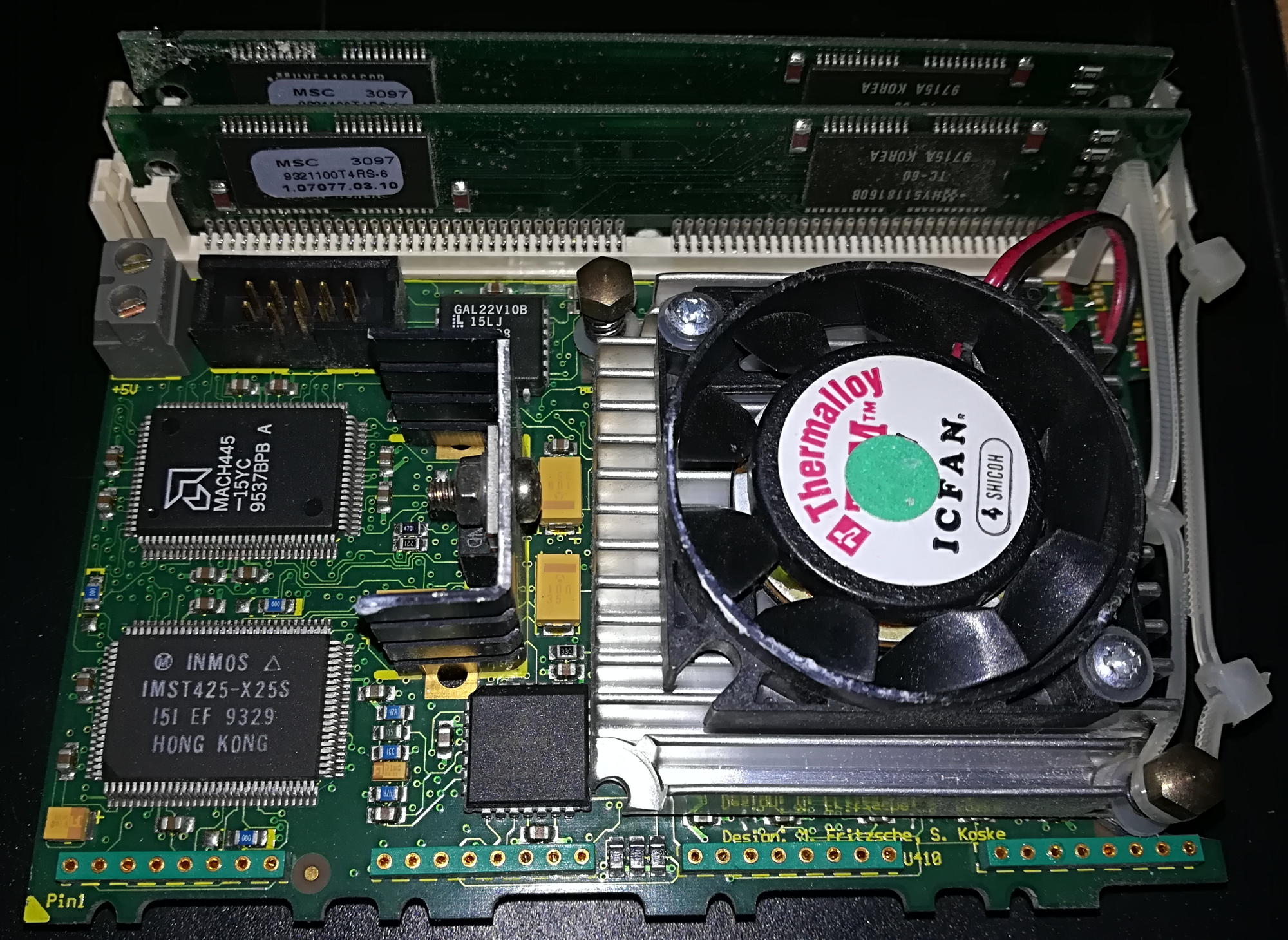

The IMS B420 featured a ZORAN ZR34325 DSP (45 MFLOPS peak) with its own 256KB SRAM besides the obvious T800 Transputer and 4MB DRAM. My guess is, that it is comparable to the Quintek QVA-T TRAM.

The IMS B421 enabled a Transputer system to talk to GPI/IEEE-488 buses … like laboratory equipment or your old Commodore Floppydrive 😉

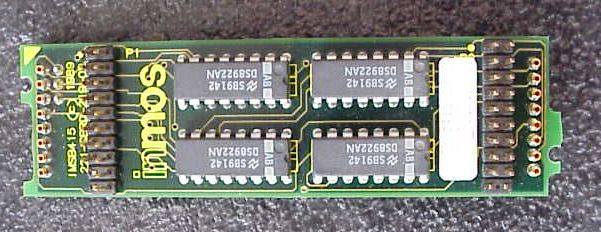

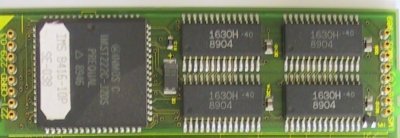

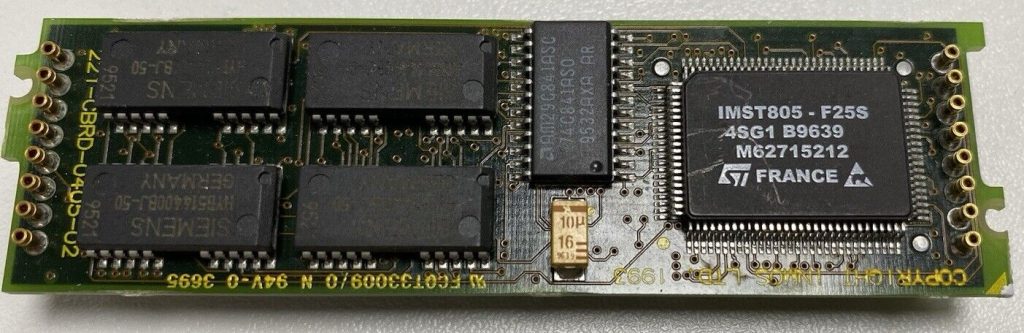

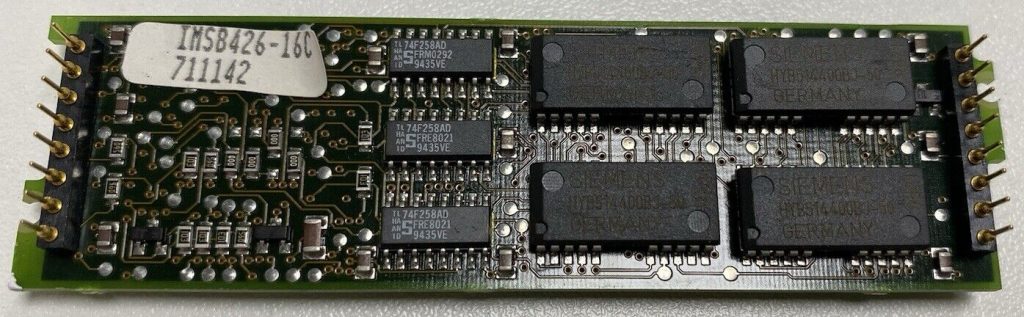

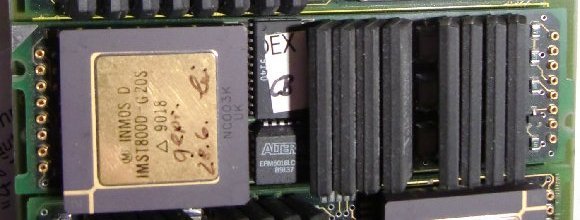

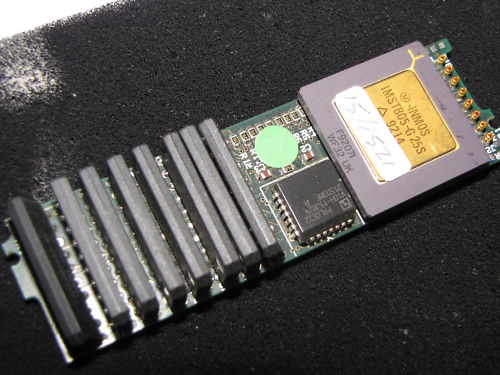

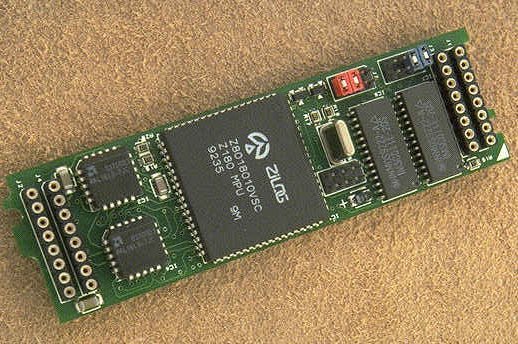

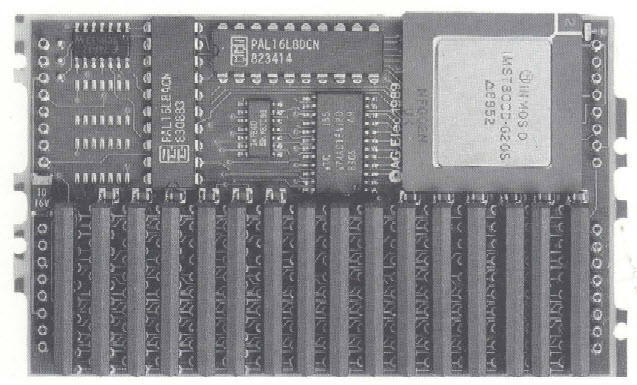

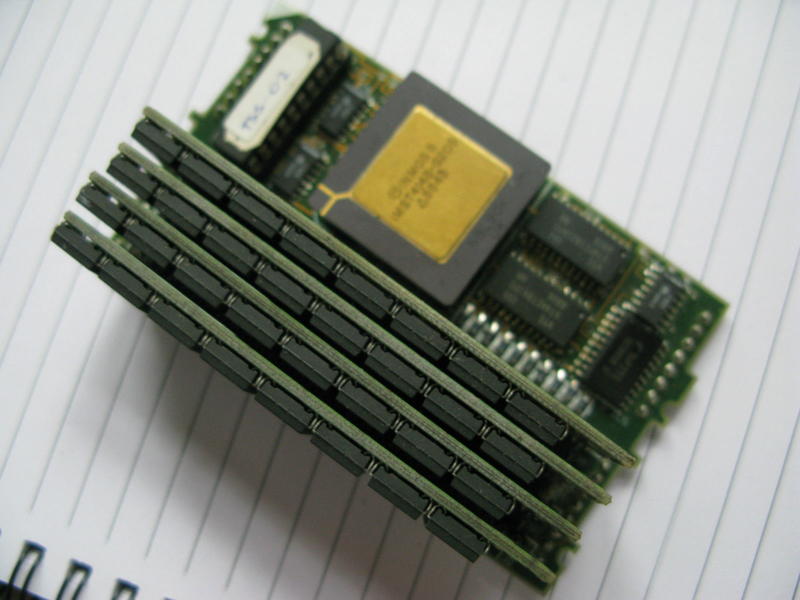

Ahh, the real-deal… the IMS B426 is what you want in your TRAM collection. 4MB RAM on a size-1 TRAM. This is where Helios really loves to run on.

…and here’s a more recent version of the B426 (rev “-16C”, 1993), this time all SMD, featuring the latest T800 in a nice TQFP case

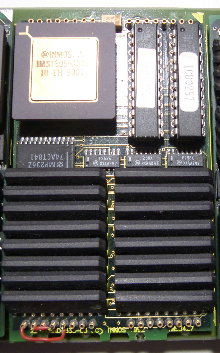

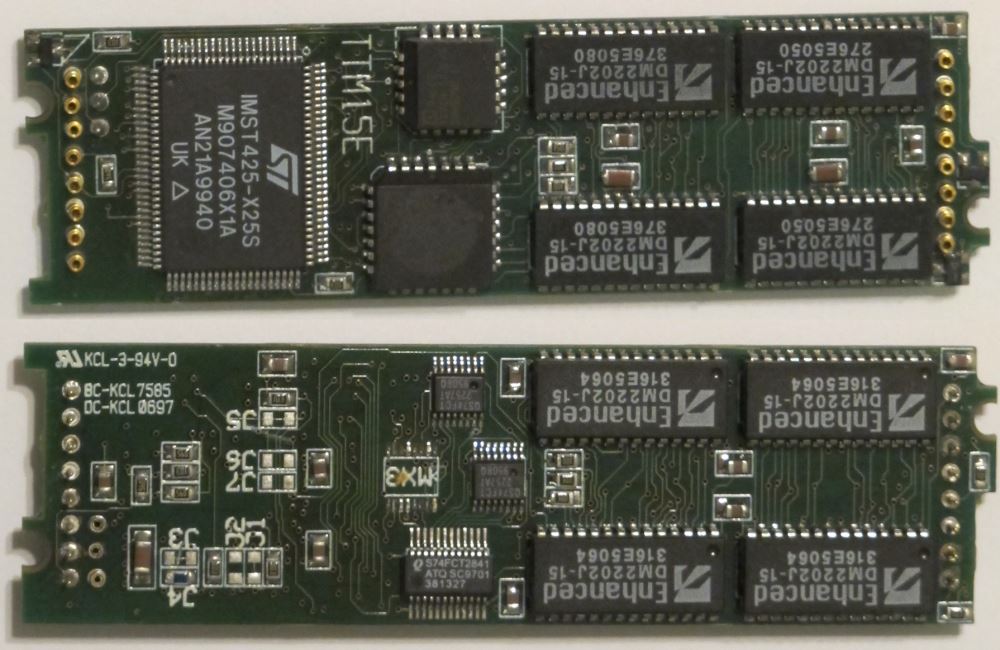

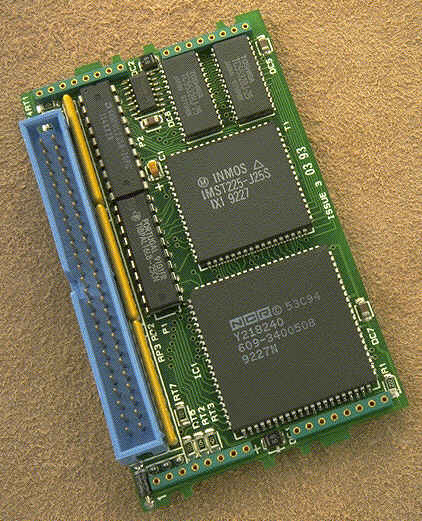

Well, the IMS B426 is great… as long as you can’t get the IMS B427 😉 This Size-2 TRAM features a whopping 8MB RAM. Enough for running Helios and X11 on it.

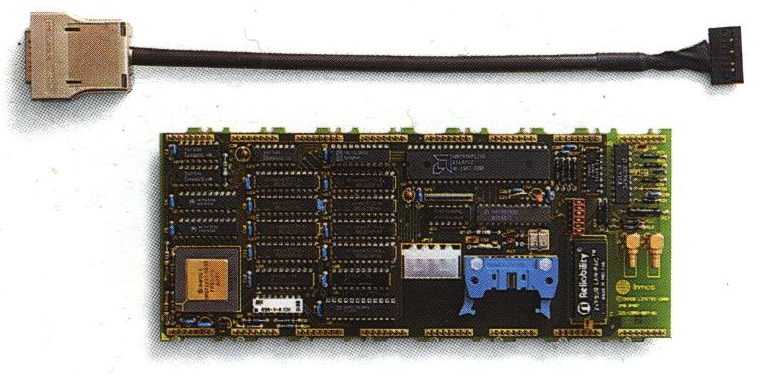

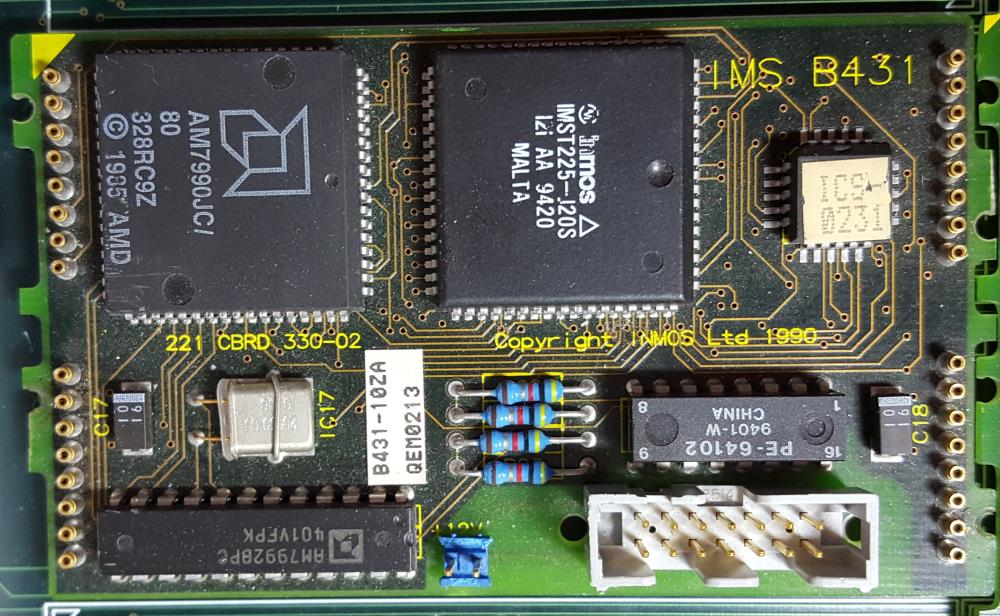

Something more important than ever is a fast network connection. The last ethernet TRAM from INMOS was the IMS B431.

10mbps is the maximum you get… well, more wouldn’t make sense given the Linkspeed of 20mbps.

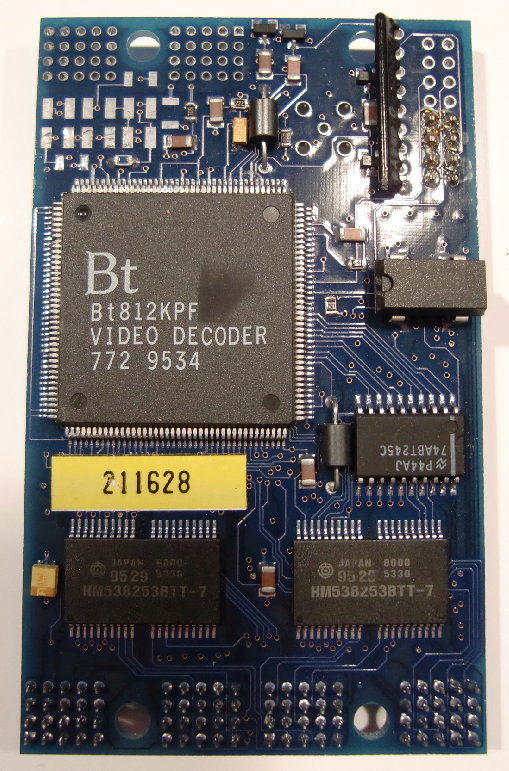

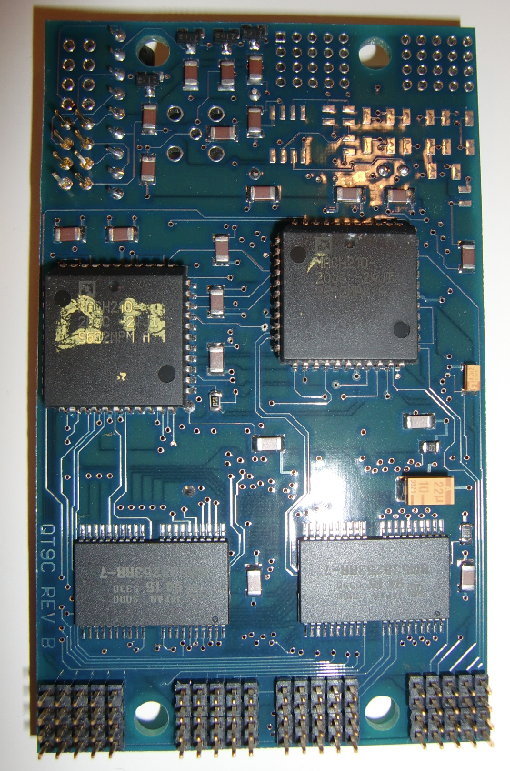

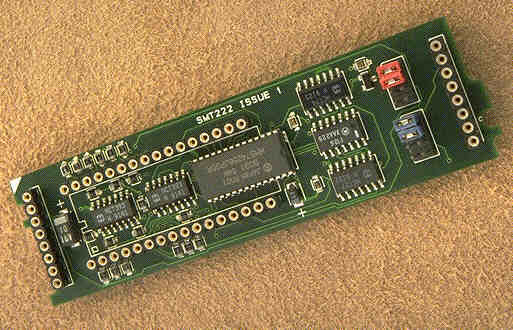

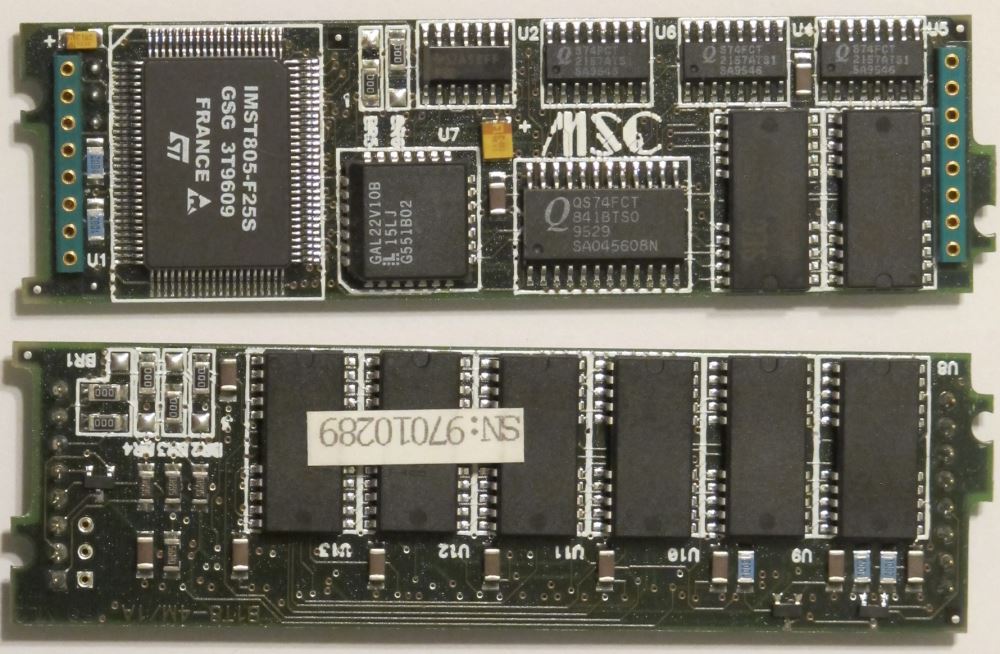

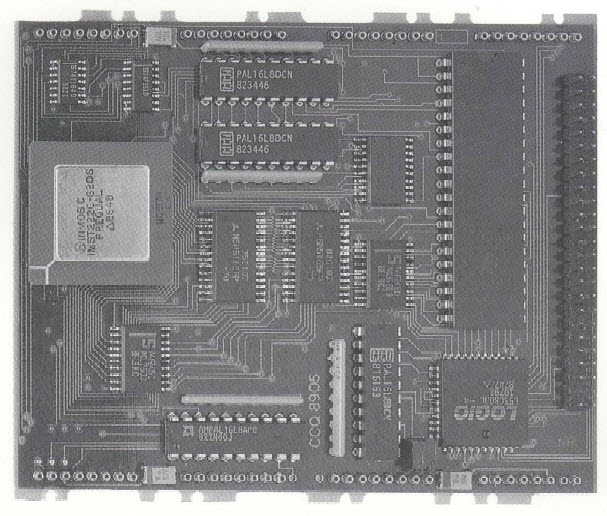

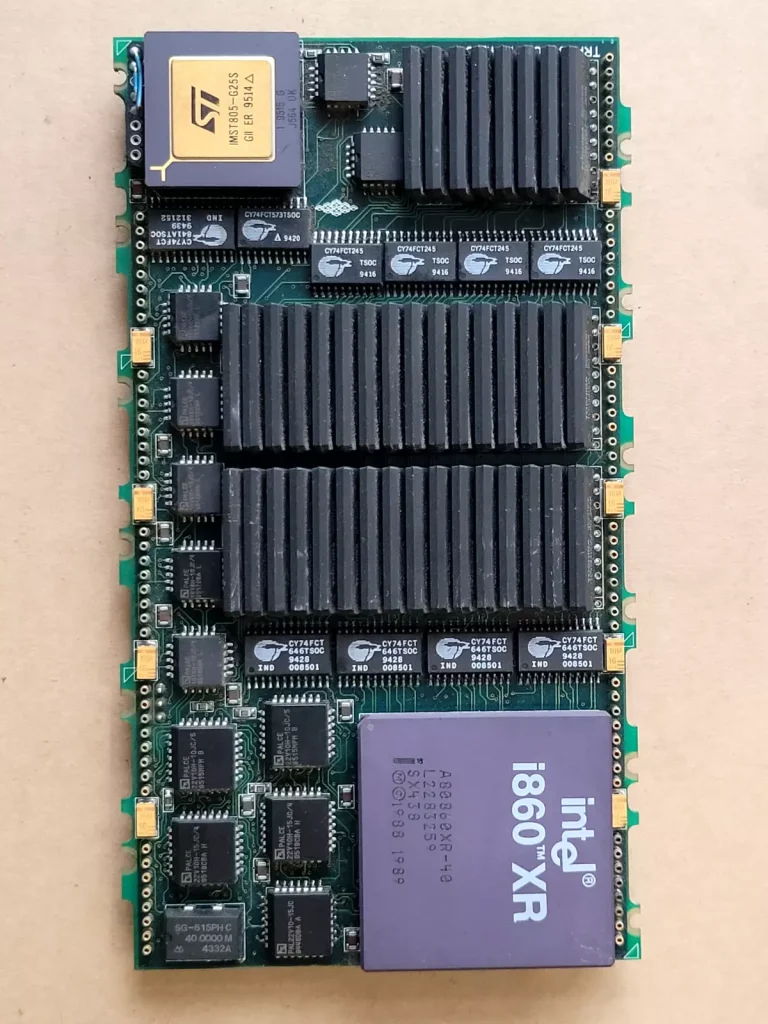

The IMS B437 is a very neat little thing: A graphics TRAM as size-2 TRAM! A nice 25MHz SMD T805 and a G332 colo(u)r video controller. Rare as chicken teeth!

It looks like this was designed by Contex Systems Design Ltd. and OEM’ed by INMOS.

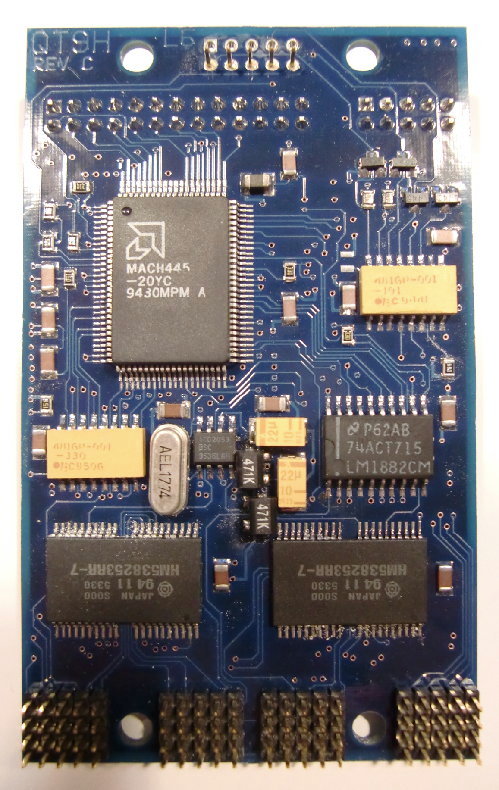

And when you thought you’ve seen them all, another one pops up:

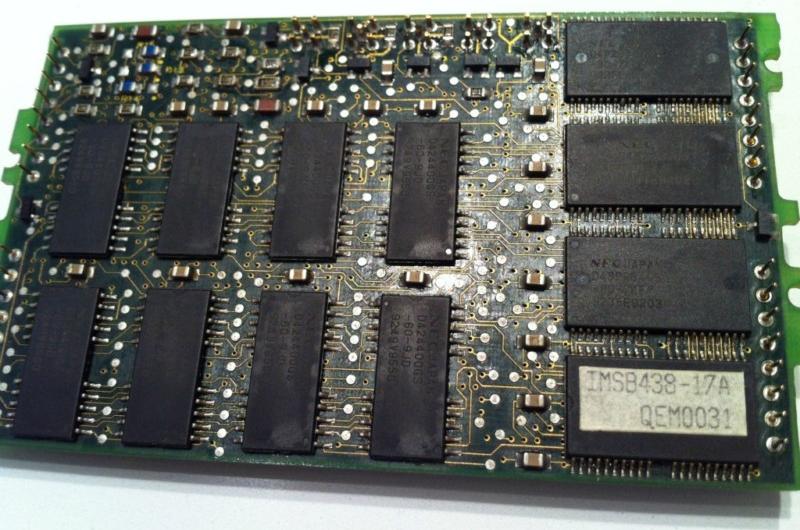

The mighty IMS B438. As the name-code suggests, it’s an updated B437 – very updated and IMHO the ultimate graphics TRAM: 2MB VRAM, 4MB DRAM, 30MHz T805 and the last and final 32Bit video controller G335@130MHz. I really, really want one. Badly!

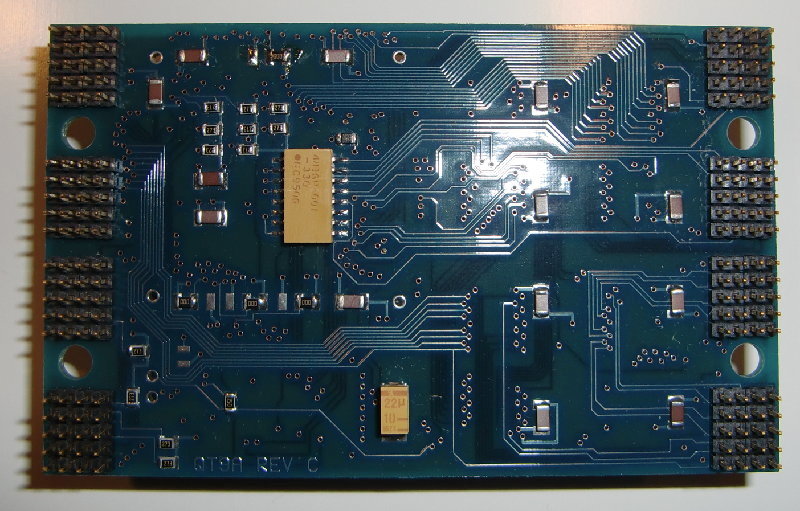

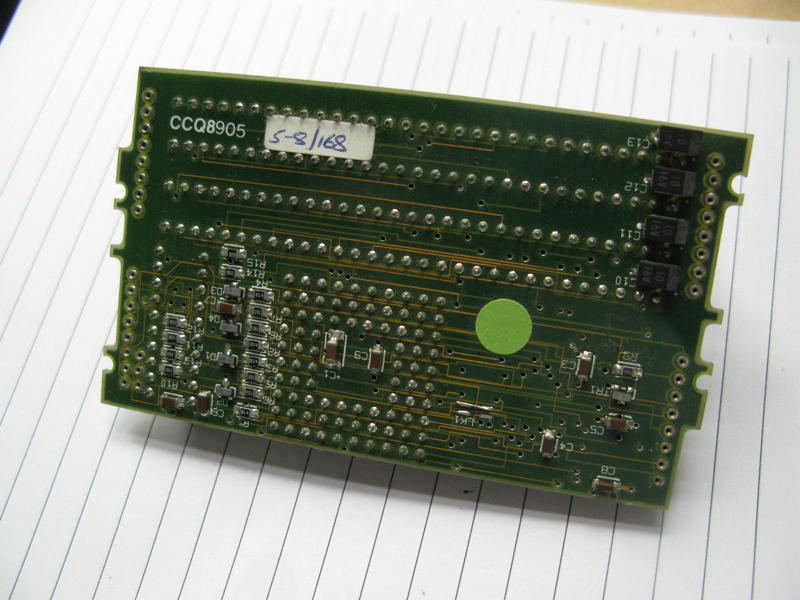

Because it’s a beauty, here’s its back, too: