This is indeed a very rare breed – I was informed that less than a 100 of those were sold. Built in the end of 1992 as “Project Zorro” by the German company miro (bought by Pinnacle in ’97) it took the same line as all the other accelerated graphic cards in those days: Highspeed graphic -mostly TIGA- plus some speedy general purpose CPU. The SPEA cards using Intels i860 were direct competitors for example – I was also told that miro also looked into using the i860 but scrapped that attempt in an early stage in favor for the HIGHRISC.

The Miro HighRisc -or miroHIGHRISC as they wrote it back then- was a full-length 16-bit ISA card containing a MIPS CPU and a maximum of 32MB of RAM.

Technical facts:

- 33MHz LSI LR33050 CPU which is a R3000 clone including the R3010 FPU minus MMU

- 1k data- and 4k instruction caches on-die

- 33 MIPS / 33 MFLOPS

- 8-32 MB RAM plugged into up to 4 SIMM slots

- 32 bit bus to connect the miroTIGER graphics card (100MB/s)

- 2D: 150000 Vectors/s of 10 pixels length

- 3D: 10000 triangles/s of 100 pixels, flat-shaded

- 6000 triangles/s of 100 pixels, Gouraud-shaded

miro claimed that the HighRisc would deliver nearly twice the performance of an i860/33 solution with “real-world” applications (namely AutoCAD 12). That has yet to be proven but sounds reasonable given the limitations the i860 had when used as general purpose CPU.

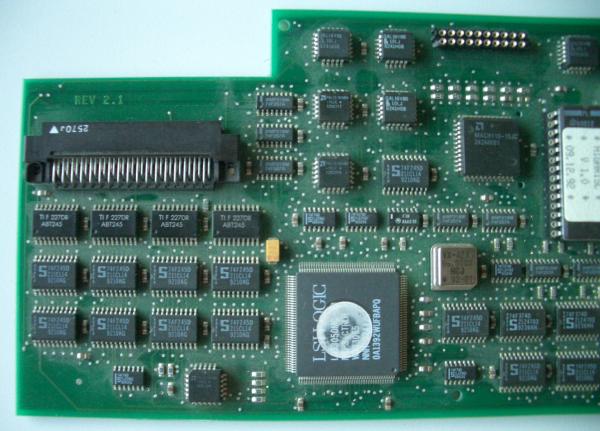

Here’s the HighRisc in its full glory:

Interestingly, there’s next to none information on the Web about this card. Probably due to its high cost (5700DM) and the failing TIGA standard.

Here’s a nice snippet from an interview (in German) from 1999 with the original product manager Frank Pölzl:

Q4. What was your biggest flop?

miroHIGHRISC, a 3D-graphic card with MIPS and TI-Graphic-Processor.

Another tasty detail is that according to a news-snippet from the German magazine c’t (12/99, p.22) this card was developed in cooperation with Silicon Graphics (SGI) which bought MIPS some years before. Maybe this was SGIs first and last attempt to get a foot into the PC market?

Yet another interesting fact: The LSI 33k CPU was later radiation hardened by a company called Synova Inc., rechristened as “Mongoose V” and as such traveled into space several times… even to Pluto!

Here’s the left side of the card in more detail. It contains the CPU and the BIOS (32k EPROM dump available here) lots of 74-logic ICs, GALs and some MACH PLDs.

At the top-left corner of the picture below you see the connector to the miroTIGER, a TIGA graphics card described a bit further down on this page.

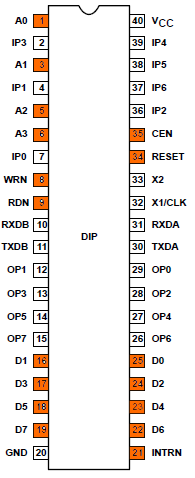

Also, there’s an undocumented 20-pin connector at the upper-right edge of the card. This might be the 16MB/s interface “to connect peripherals like laser printers or repro-devices” as mentioned in the c’t article. Thinking about it – it’s an interface to an UART. This will be a nice project to do further investigation.

The pinout (the connector is rotated 90° clock-wise):

GND oo /WR0

D0 oo INT2

D1 oo /RD

D2 oo /IOSEL

D3 oo (unknown)

D4 oo A2

D5 oo A3

D6 oo A4

D7 oo A5

VCC oo A23

The right side of the card is dominated by the 4 SIMM slots which, according to the manual, support up to 8MB each. Also there’s a DIP-switch for setting up the address-range etc.

Even it has nothing to do with MIPS, the accompanying graphics card miroTIGER fits in quite good here. This card was meant to run for itself or accelerated by the above described miroHIGHRISC. This is what it looks like:

Following the TIGA standard it naturally features a TMS34020 graphics processor. This processor has its own RAM to do all the calculations, display-lists and fonts. Because TIGA was completely incompatible to the usual CGA/EGA/VGA standards you had to have such a card installed in parallel to see all the DOS/Windows outputs before switching into TIGA-mode. The normal setup was to have a 2nd high-res (1024×768++) monitor connected to the TIGA card then.

More advanced cards like the miroTIGER also had a VGA chip on-board, which saved you a slot and all the extra hassle. So let’s have a look at the details:

This is the left side of the card. The nice golden chip is of course the TIGA processor. Next to it there’s a National Design V2000 chip – most probably an ASIC doing all the RAM handling and stuff.. accidentally I stumbled across a notion of a “National Design Volante2000” TIGA card. Smell the relation here? So my most recent assumption about this is, that’s a somewhat standard TMS340 glue-chip, licenced by National Design to other TIGA card manufacturers.

The SIMM above is 8MB of RAM for the TMS340. Depending on the PAL (labeled 2004, 2044 or 2084) on the lower edge of the card, one could use 0, 4 or 8MB of RAM.

On the upper left corner is the connector to the miroHIGHRISC card as well as an impressive row of DIP switches.

The right side is mainly occupied by 4MB VRAM for the TMS340 as well as the TI RAMDAC in the upper right corner.

Below is a very simple onboard VGA controller by Cirrus Logic (CL-GD5401 aka Acumos AVGA1) and next to it its puny 256k DRAM – which is the maximum a GD5401 can address by the way :-/

This is a good place to post a big thank you to Peter Huyoff – the wonderful guy who saved my life while doing the ‘research’ on this card.

As you might spot in the picture above, there’s one chip broken… a tiny 74AS74 flip-flop – try to find a single SMD AS74 these days. It’s impossible if you’re not prepared to pay $50 b/c of minimum order fees! And no, an F74 doesn’t do it, it’s still too slow. Been there, done that.

Peter provided me another working miroTIGER for free! That’s the spririt between real men! And Peter is definitely one of them!