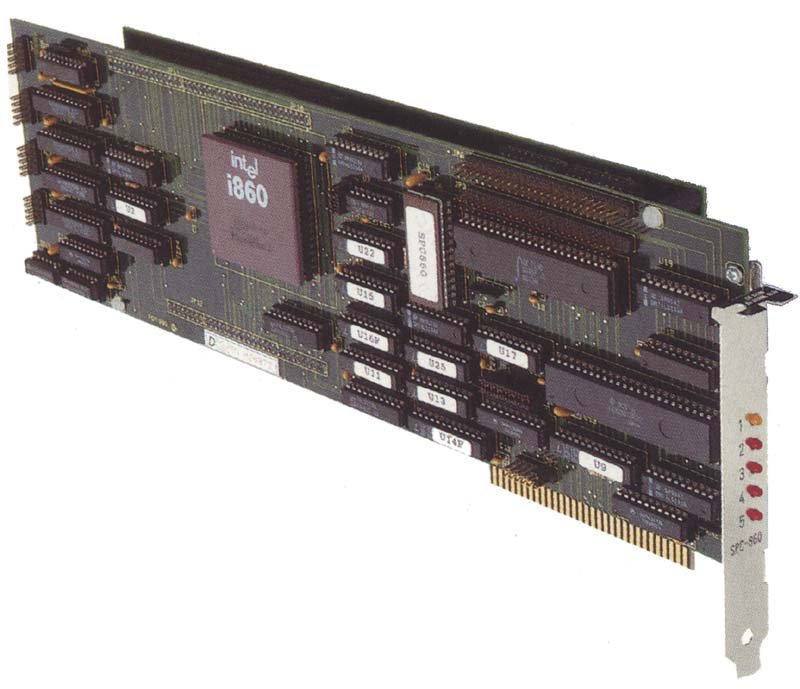

Based on a public project from Rolf-Dieter Klein and Tobias Thiel (“PC-Karte mit i860”) in the German computer magazine “mc” (2/90 to 7/90), the Munich based company DSM built several i860 boards for the PC/AT which they called the DSM-860 series.

All DSM-860 have one thing in common: They offer a high level of hardware features – no costs were feared. So naturally, those cards were not cheap. But you really got something for your money. All versions featured

- 4 Transputerlinks for networking multiple cards

- Connection to the hosts system-bus (ISA/EISA) via dual-ported RAM

- A 16-bit bus is also available via dual-ported RAM on special connectors giving a throughput speed of 8MByte/s for high-speed connections between several SPC boards.

- RAM was put on an extra RAM board making the complete SPC-860 a double-card sandwich

DSM-860

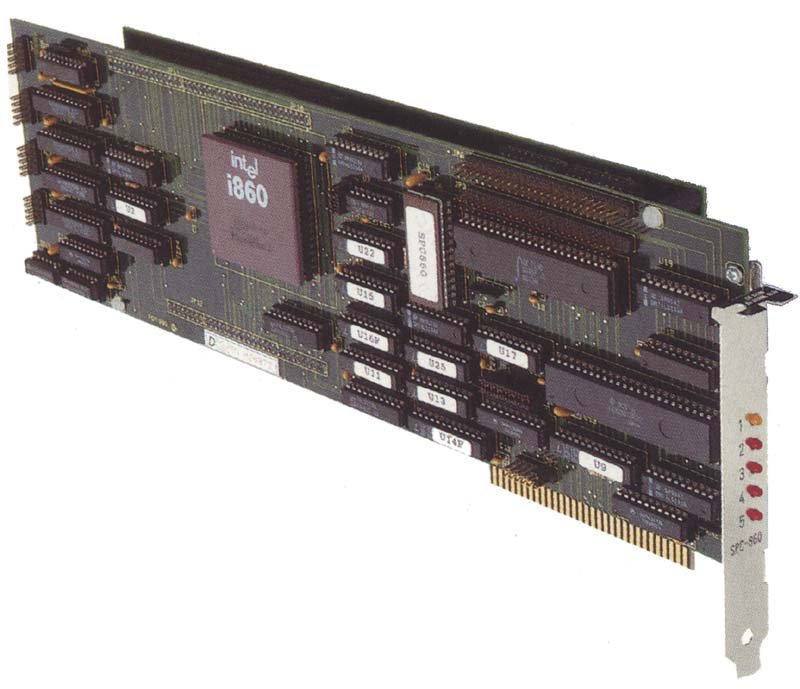

The 1st incarnation was the SPC-860, very quickly renamed to DSM-860, an 8-bit ISA card with 4MB RAM (DIL) and 4 10mbps Transputerlinks via four C012’s (polled by the i860 resulting in 740kbps linkspeed).

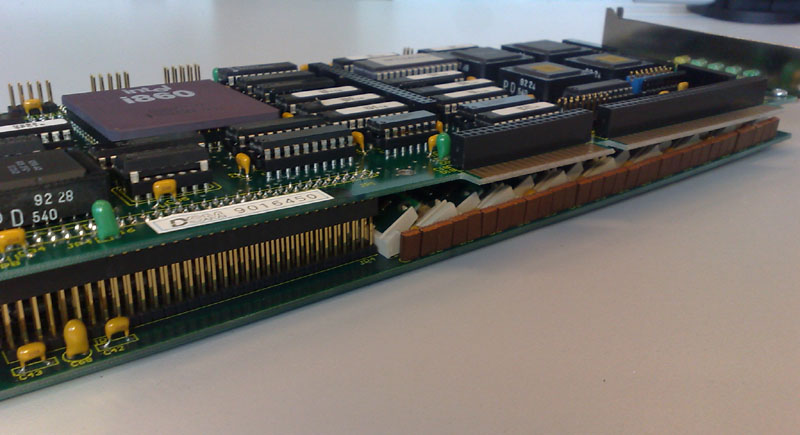

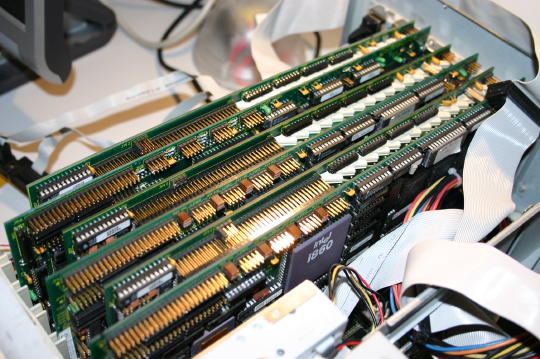

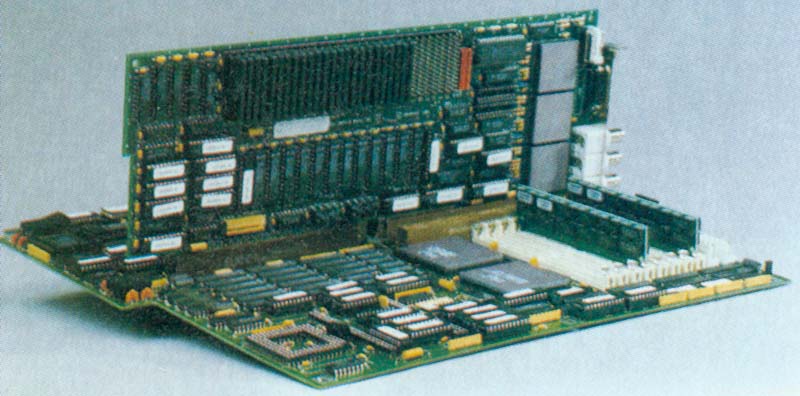

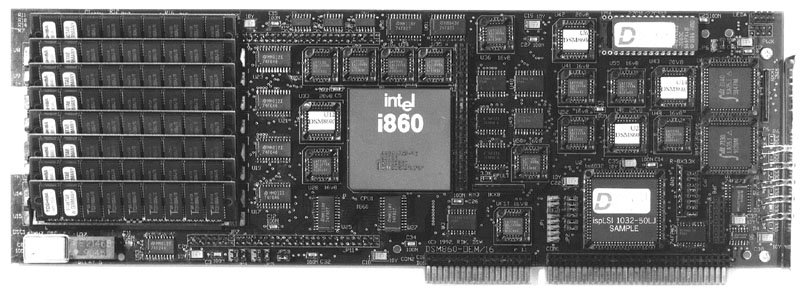

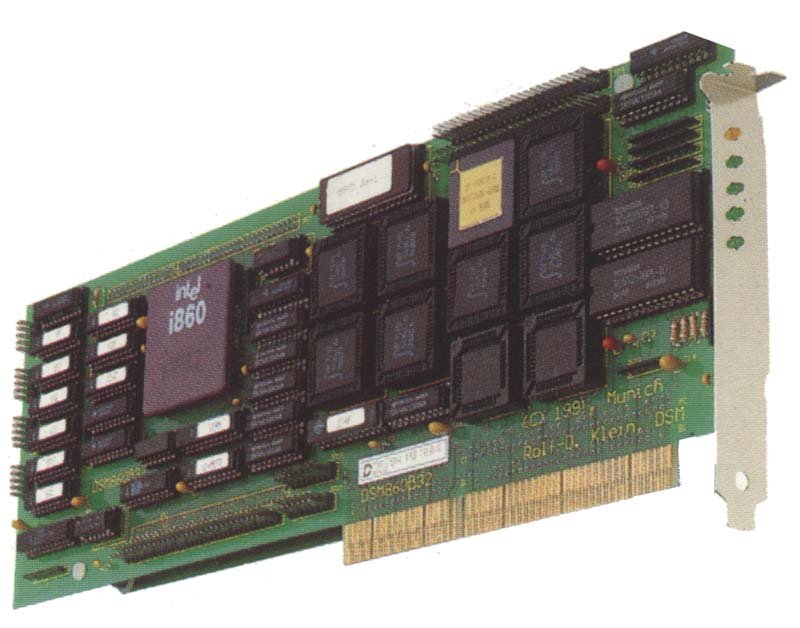

Here’s a picture from a 1992 ad, with separate RAM card attached:

It did cost 16450 DM including the (GNU) C compiler and assembler.

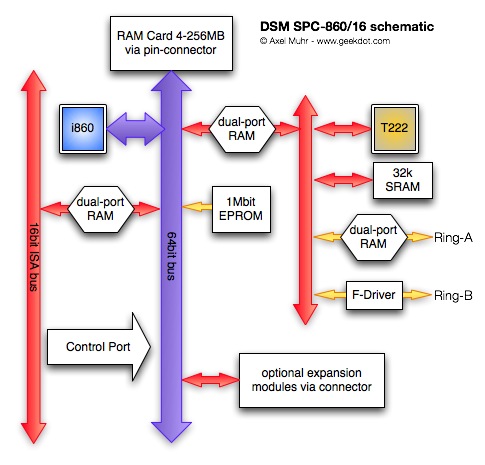

DSM-860/16

Next, they released the DSM-860/16 (renaming the DSM-860 into DSM-860/8) being a full fledged 16-bit ISA card. It has a real Transputer (16bit T222, having its own 32K SRAM) for handling the “multiprocessor communication” and is able to support up to 256MB on a sandwiched daughter-board, now using SIMM modules instead of DIL parts.

The Hitachi HD63310 dual-ported RAM, used in the 8-bit version to communicate with the host was replaced by faster Cypress IDT7130 types (“because of the high speed of the 16-bit ISA interface” ;-)), resulting in a peak-rate of 14MByte/s.

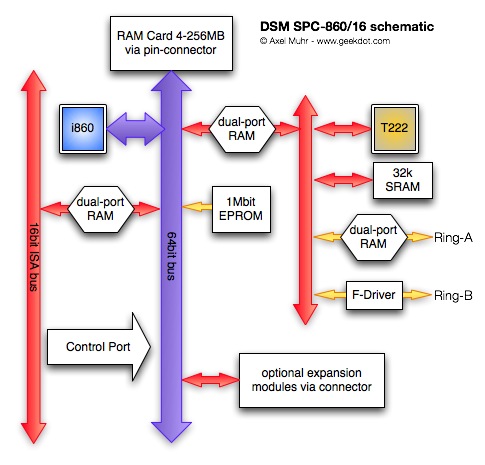

Here’s the schematic of the card and its components

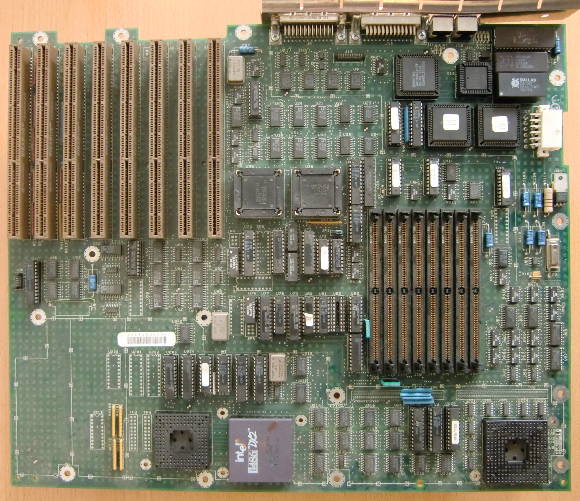

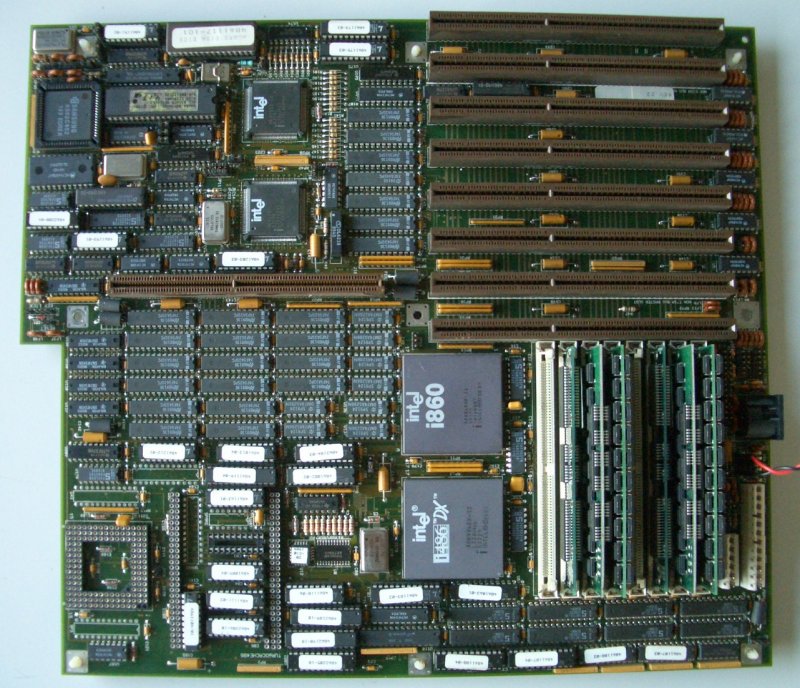

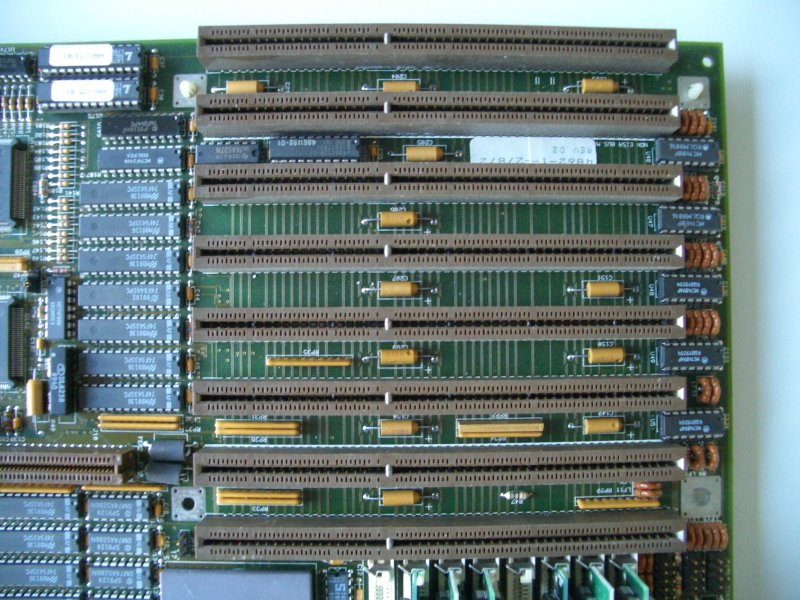

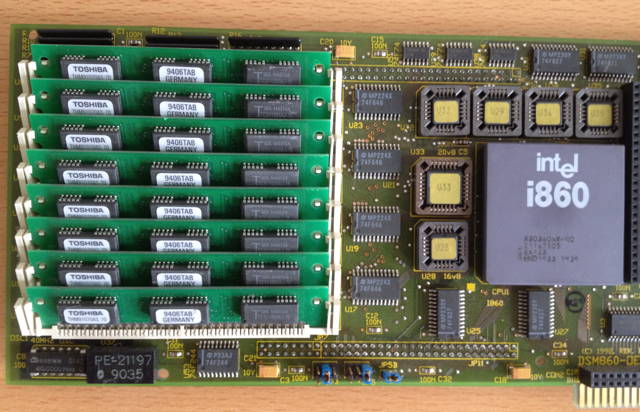

This is how it looks in reality… my DSM-860/16:

As you can see, the card is not exceptionally high integrated – even built 1992 there is not a single SMD part used, everything is socketed, only some PALs could be called “custom parts”. But this does not necessarily mean it’s badly designed or build.

If you have a close look (click the picture for a bigger version), you’ll see that every part/socket/jumper on the board is nicely specified in the silk-screen printing. All GALs and the EPROM contents are available in the documentation… which has 426 pages by the way.

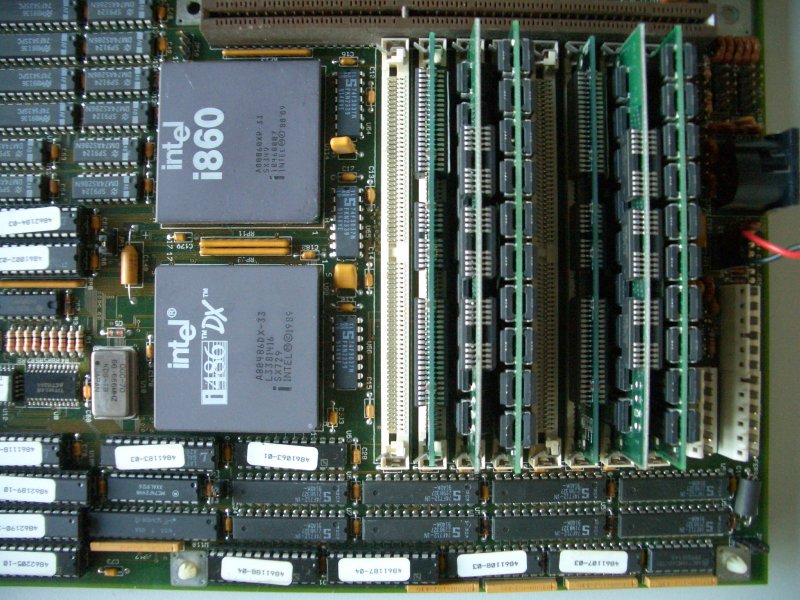

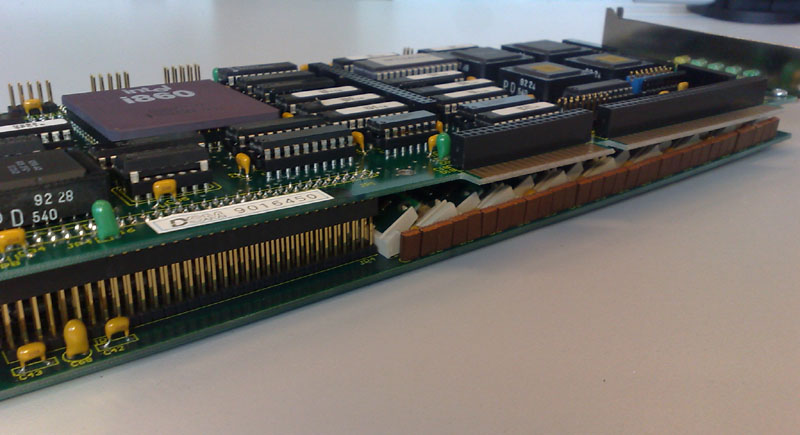

Here’s the left side in more detail:

This end of the card is the “external comms” side. Beside the all-mighty i860 you can easily spot the golden Transputer being the communication controller.

To its left, there’s the first dual-ported RAM (1k x 8) connected to the socket for the external bus (Ring-A, located on the edge above). Below that are the two 16k SRAMs -marked MHS- for the Transputer. Then to the right are the two dual-ported RAMs (a 7C131 and a so-called slave 7C141) making the 16-bit connection to the i860’s bus. The rest of the parts are quartz oscillators (5MHz & 40MHz) and drivers/buffers for the buses. On the top edge next to the Ring-connectors you can spot the 4 Transputer links (JP9-12).

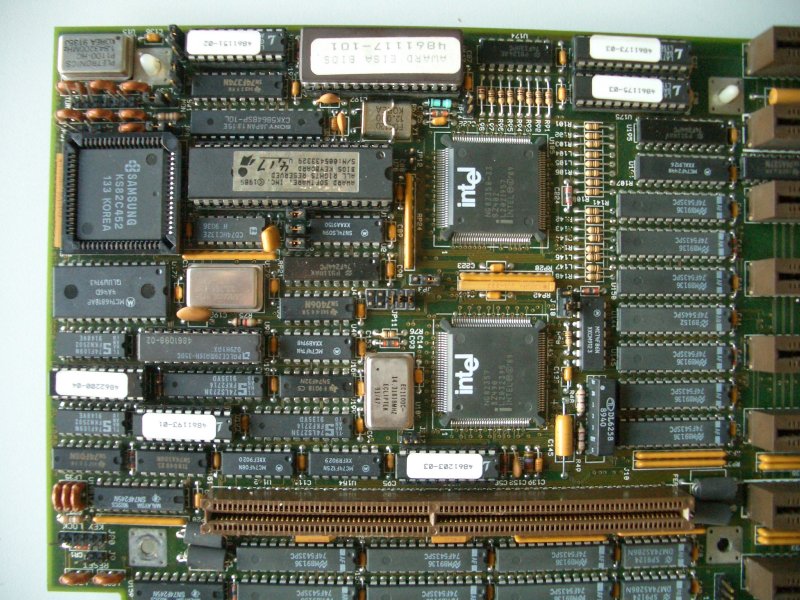

The right side is comparably boring:

The boot EPROM, 6 GALs, again two dual-ported RAMs (this time for the ISA-bus connection) and some buffers… well, and 5 LEDs. LEDs are good. 😉

Also, you can see the pin-row connectors at the lower edge and on the left of the photo. That’s the expansion-bus. The lower connector is more or less 1:1 the ISA bus, the left one is a 16-bit bus to the i860. AFAIK, they never offered an expansion for sale.

The last (but not least) interesting thing on this picture is the copyright. Yes, it’s a DSM860/16 from 1992, RDK made it (Rolf-Dieter Klein), DSM in Munich distributed it – but it’s obviously also a rev. 1.6, which means there could be others before or after that one. If you have more informations I would be happy to learn more.

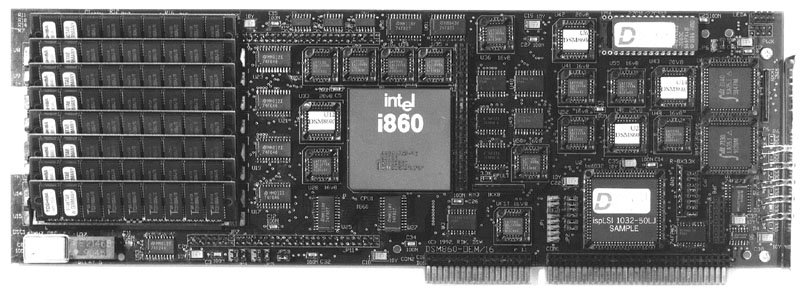

DSM860-OEM/16

I’m pretty sure there was one more version after this rev.1.6, this b/w picture from a DSM press release about shipping the 250.000th slot-CPU card shows a very changed design. The silkscreen print says “DSM860-OEM/16”, so it’s obviously nothing for the normal market.

Mind the onboard-RAM, the missing comms-section and the high integration (SMD parts all-over) and even an early form of an FPGA from Lattice – my assumption is that this version could be the answer to the Kontron SBC860 showing nearly the same layout:

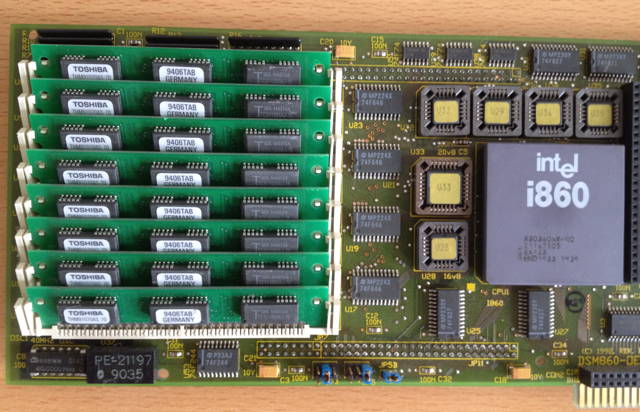

At least this ‘riddle’ is finally solved. I was able to buy an DSM860-OEM/16..Yay! As assumed, it is a modern (for 1990 standards) version of the DSM860-16 now consisting of just one board, so no more RAM card as described below- and without the Transputer and Ring-A/B stuff.

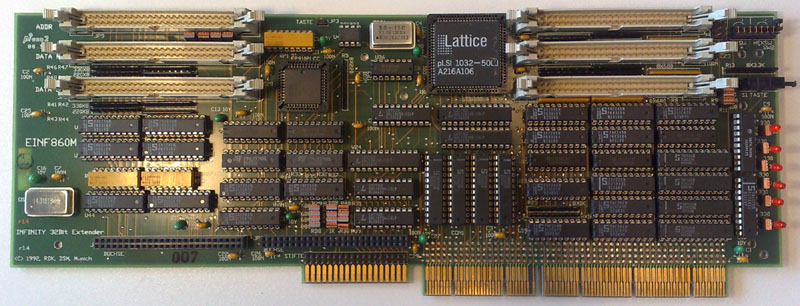

Here are my pictures of it. First of all, the card in full view:

The right half shows a very high degree of integration compared to its predecessor. All DIL ICs were replaced by SMD parts and lot of logic went into PALs and even an FPGA (The contents of the EPROM is the same as with the other card, minus Transputer handling):

The left half contains the CPU and the RAM. This time only 8 SIMM slots:

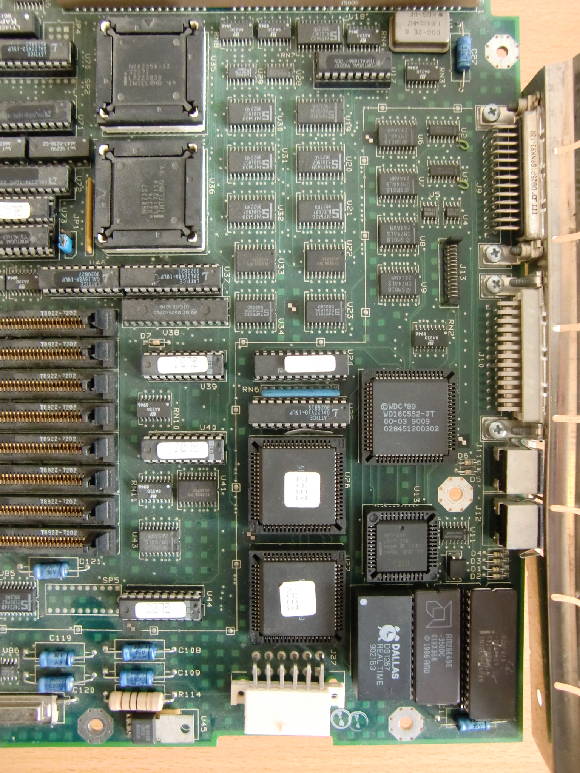

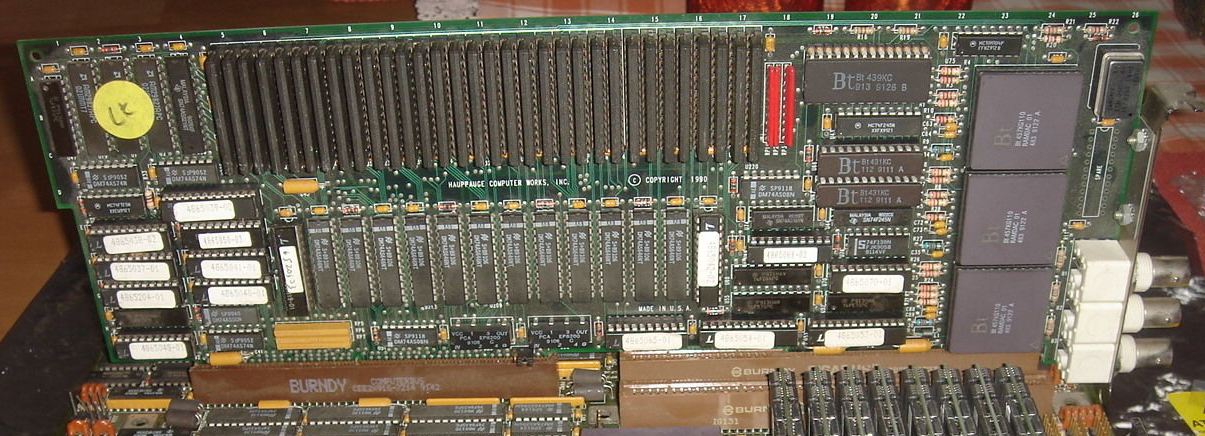

The RAM card

This is the 2nd part of every DSM-860 – the RAM card (except the OEM-16). Same dimensions as the SPC itself… i.e. full length. The biggest part of it is consumed by the 16 angled SIMM sockets, obviously interleaved, thus named altering slot-a & b. Only the 8 a-slots are populated on mine.

The rest of the board is used for lots of buffers and drivers, some GALs (doing the mem-mapping) and there’s quite a big copyright… again.

One typical detail of those days is the fact that manufacturers were not very keen on having users doing upgrades themselves. Even this RAM board has standard SIMM sockets and one could simply plug in more SIMMs to expand the RAM you had to change a GAL (the one in the lower left corner with a while label saying “UXM24Wxx” on it). Obviously these GALs are the only ones notdocumented. All I know is that there were 3 GALs available differing in the last two letters of the label:

- 8B = only a-slots can be used by either 1M or 4M SIMMs giving 8 or 32MB total

- 16 = both a- and b-slots used with 1M SIMMs = 16MB total

- 64 = a- and b-slots filled with 1M and/or 4M SIMMs giving 16, 40 or 64MB total.

Because the card as well as the documentation says the maximum supported amount of RAM is 256MB there might be the chance of supporting 16MB SIMMs – I did not try this yet.

Both cards attached together give quite a big and heavy sandwich

It’s obvious that you not only need 2 full-size slots but also guide-rails inside the case to hold the weight of this beast.

DSM-860/32

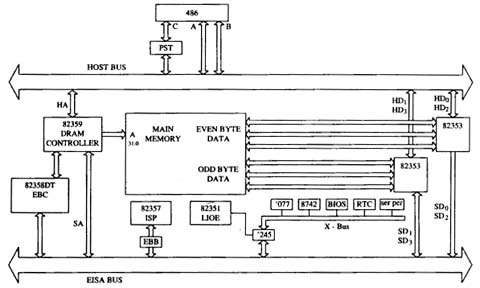

This seems to be the king of the SPC hill. Technically it’s pretty much the same as the DSM-860/16 but this time featuring a 32-bit system bus – namely EISA. The EISA bus was a dead-end like IBMs Microchannel but comparably easy to implement and free of license fees.

So the main difference to the DSM-860/16 is the 32-bit wide connection to the hosts bus, visible by the 4 dual-ported RAMs used for a 32-bit wide connection to the EISA slot.

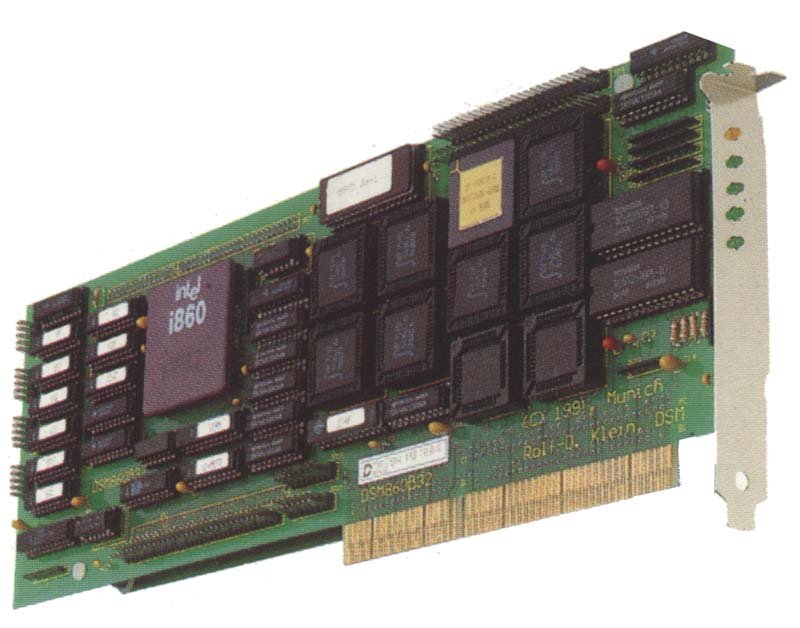

Again, here’s a 1992 magazine ad showing a probably early version of the card as the marking says “DSMß860-32” (mind the beta) and the year “1991”:

Compared to that, my version (1.2) does not look that much cluttered – also the Transputer comms part were moved to the left side of the i860 and two more LEDs were added:

So the left side of the card looks pretty identical to the DSM860-16, while the right side has a bit more logic to satisfy the EISA standard, the already mentioned 2 more DP-RAMs, a bigger expansion-bus due to the EISA slot and most important: 2 more LEDs! Did I mention that LEDs are good? 😉

This more detailed picture shows that the DSM860/32 was released the same year as the ISA version. This card is a rev.1.2 – again, if you know more about revisions, I’d be happy to hear from you.

You might have spotted that this card looks a bit shabby. That’s because it was pulled from some universities dumpster. It was missing some components and had some “scars”. The good thing was that none of the GALs were missing and due to the fact that every piece is documented on the card it was easy to replace the missing parts.

On the above picture you can clearly see e.g. the 100nF capacitor C40 below the i860 or the 40MHz OSC. I wish everything would be that well documented.

The Infinity card

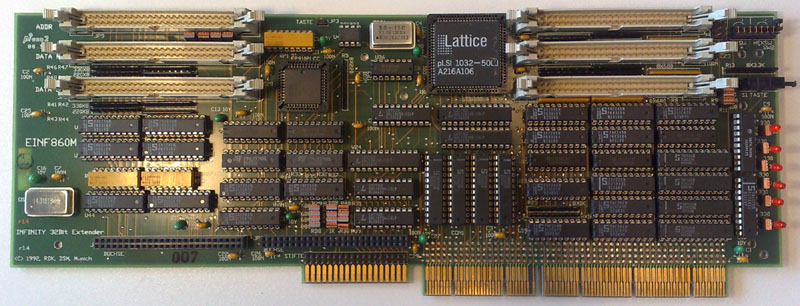

This is a rare and mysterious beast. The documentation only touches it very briefly. It’s definitely nothing been built for the average DSM860 user – if something like that existed. For sure it was extremely expensive… and it has LEDs 😀

So at the first look you see 2×3 connectors for 40pin cables – the same used on the DSM860 cards (Ring-A and -B). Then there are a lot of drivers and buffers and a big Lattice pLSI 1032-50 which is a 6000 gates PLD (Programmable Logic Device). A closer look to the board gives more hints – thanks to the DSM (or RDK) habit to print as much info as possible onto the board:

Ok, first information we get is that this is a EINF860M or INFINITY 32Bit Extender. It’s like all other boards (c)1992 by DSM Munich and -as one would expect- designed by Rolf-Dieter Klein (RDK).

The three connectors are labeled ADDR(ess), DATA MSB (Most Significant Byte) and DATA LSB (Least Significant Byte).

The the right of the connectors is an Intel 85C098-20. I think that’s a One-Time-PLD, not 100% sure.

My educated guess is that this card is what the print on it says: A bus extender. Using the 16-Bit bus on the DSM860 cards one can build quite a big parallel computer. But the max. length of the flat-cable to connect each card with the next one is limited. So this card would be connected to other DSM860 cards in the same case (i.e. a 19″ case in a rack) and the extender would then “amplify” the bus-signals to be send over into the next rack full of DSM860 cards.

That said, my fear is, you’ll need two of those cards as the seperation of Adresses and Data (MSB and LSB) is nothing being used on the DSM860 cards. So my next guess is, that the INFINITY communicates over the EISA bus with the other cards and has its own external bus. Again – I’m happy if you contact me if you know more/better!

Nostalgia

And here’s a full page ad I found in my old (German) computer magazines – it shows all 3 versions: