After 7 years mainly doing research on Transputers and the i860, I had the feeling it’s time to do some more digging into the highRISC card.

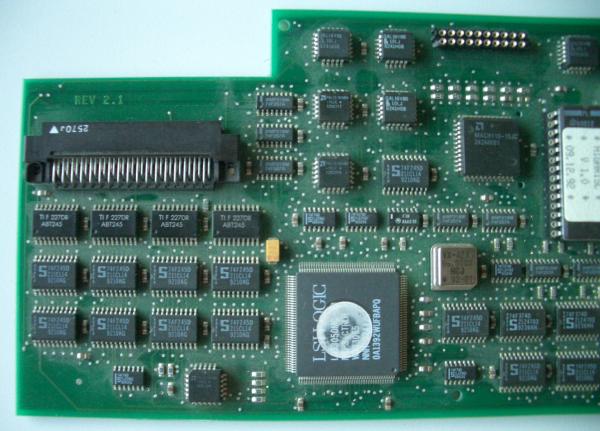

If you have read my initial post about the miroHIGHRISC (and the Tiger) you remember the undocumented 20pin socket on the card (pictured in the upper right corner):

Let’s have another look at the “UART port” again:

The pinout (the connector is rotated 90° counter clock-wise):

GND oo /WR0 D0 oo INT2 D1 oo /RD D2 oo /IOSEL D3 oo RESET (most likely) D4 oo A2 D5 oo A3 D6 oo A4 D7 oo A5 VCC oo A23

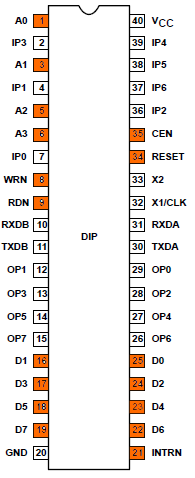

Reading a bit of the BIOS’ disassembly, I stumbled across routines to talk to an UART. A very common (D)UART of those days was the SCN2681. If you take a look at this chips specs, they perfectly fit to the signals provided at the HIGRISCs UART-port!

Here’s its pinout with the corresponding pins marked:

A2-A5 are used for A0-A3 on the 2681 and the only pin not directly represented is A23 which might be used to decode. Also, it nicely reveals that CPU INT2 is used for the UART.

The LR33000 datasheet tells me that there’s an 4MB IO-area starting at 0x1E000000 reaching up to 0x1EFFFFFF- most likely the 2681 will live there… and the corresponding signal called /IOSEL is available on the UART-port (and will perfectly help as chip-select decoder). Tadaa!

So after the UART we need to get the RX/TX signals to a higher level, i.e. the +/-15V of RS232 – this is the call for our old friend MAX232.

[current bread-board experiments sadly didn’t yield into ‘instant success(tm)’… I’m missing out something – need more time to investigate]

Bootcode / BIOS

The LR330xx CPU also has an /EPSEL EPROM select signal, indicating it’s accessing an EPROM expected to start at 0x1F000000 and ends at 0x1FFFFFFF (4MB right below the IO-area).

Using this knowledge and knowing that the MIPS standard boot-vector is at 0x1FC00000, it’s easy to feed the ROM-dump I did some years ago into the disassembler with the correct start address to do his job.

We need to get an understanding of this bootcode first, so that we can get an idea of “what is where” (e.g. ISA bus, UART etc) and later upload our own code and use those addresses.

Just to stick my head a bit into the clouds, the aim is to first port a then common MIPS monitor-program called ‘PMON’ and use that to run some sort of μLinux. But that’s probably another handful of years ahead…

PMON was a good source of information, because it’s originally written by LSI, supporting all the LSI eval-boards. Lo and behold, some of them had a 2681 UART, too… located at 0xBE000000, which is extensively used in my BIOS disassembly 😉

I have a certain feeling that miro borrowed some design ideas from the LSI Pocket Rocket evaluation board (don’t Google it, it’s a mythic being – if you have documentation, mail me!).

So this is the 2681 memory-map then:

#define BASE_2681 0xbe000000 #define SRA_2681 ((1*4)+BASE_2681) // 0xbe000004 status register #define THRA_2681 ((3*4)+BASE_2681) // 0xbe00000C Rx/Tx holding register #define ACR_2681 ((4*4)+BASE_2681) // 0xbe000010 Aux contrl. register #define ISR_2681 ((5*4)+BASE_2681) // 0xbe000014 interrupt state register #define CTU_2681 ((6*4)+BASE_2681) // 0xbe000018 Counter timer upper #define CTL_2681 ((7*4)+BASE_2681) // 0xbe00001C counter timer lower #define START_2681 ((14*4)+BASE_2681) // 0xbe000038 start timer #define STOP_2681 ((15*4)+BASE_2681) // 0xbe00003C stoptimer

Using those addresses we should easily identify the comms routines.

Something happens at 0xBE800000 which seems not UART related. So that’s probably the reason why A23 is available on the connector. That way we can ignore access to that address by OR’ing it with /IOSEL to create a /CS.

The DOS side of things

The tool to load a MIPS executable into the HIGHRISC is called DL.EXE. Loading the test-program prints this to the console:

miroHIGHRISC download program. V 1.00 (c) miro Computer Products AG , Germany CONFIG: I/O-register-address: 0x368 CONFIG: DRAM - base-address : 0xD000 CONFIG: DRAM - size : 8 MB CONFIG: TIGER - RAM - size : 8 MB Resetcount = 87340 Loading test.zor text : start=0x80030000 size=0x52c0 data : start=0x800352c0 size=0x520 bss : start=0x800357e0 size=0x150 entry : 0x800301a0 TIGER comm.address : 0x3ffd00 max_used_address : 0x35930 real_DRAM : 0x800000 Heapsize : 0x7CA6D0 test.zor sucessfully downloaded.

This gives us valuable information. The DOS-side uses the IO port 0x368 and has a memory window of 16K from 0xD000 to D3FF.

MIPS programs are loaded to 0x80030000 and the 16K seems to be mapped to 0x003FFD00, just 128K below the 4MB boundary of the LR33k address space.

As usual – this is heavily work-in-progress. So this post will be edited while making any new progress. TBC…