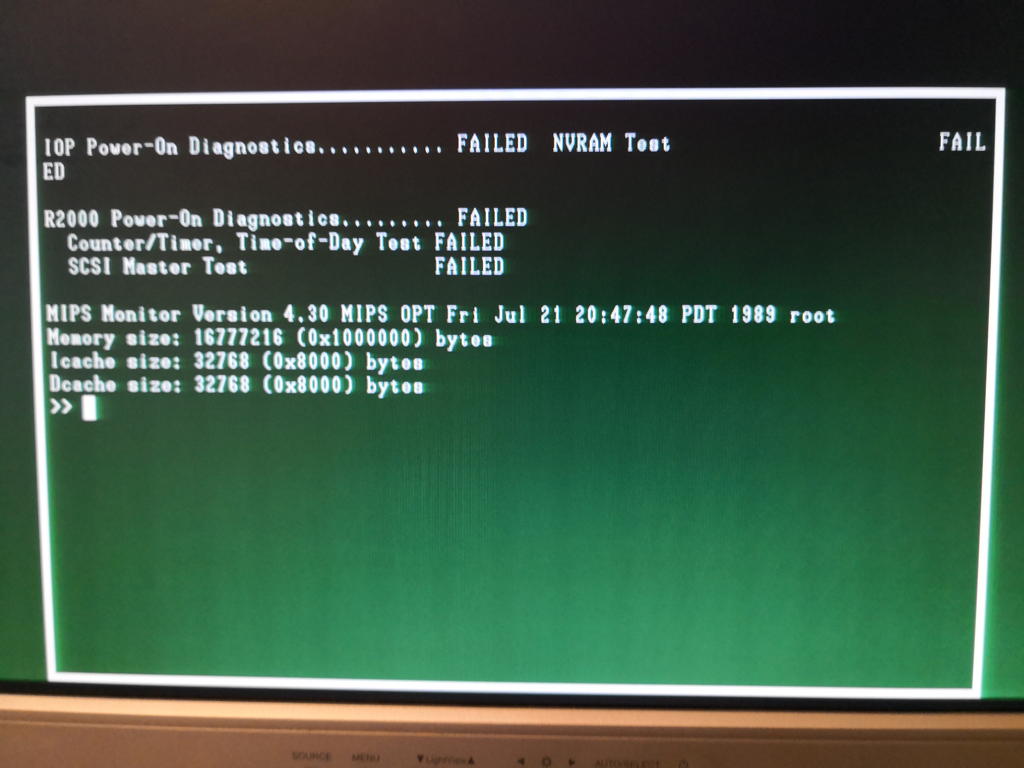

This is the last post about improvements for the MIPS RS2030 – but it will be open-ended and updated as time/project goes by.

After the resurrection of this little workstation I still wasn’t totally satisfied. As said, the console is a strange 2/3 box and obviously running in an unaccelerated slow-scrolling graphics mode – every 80286 PC console is faster.

So for starters, I switched to a remote session. Luckily the network-setup was, while yet primitive, very easy. Definitely sufficient for telnet and ftp – remember, we’re roughly in the year 1990 and the world is pretty much black-hat-free… and so is my LAN, so I don’t care.

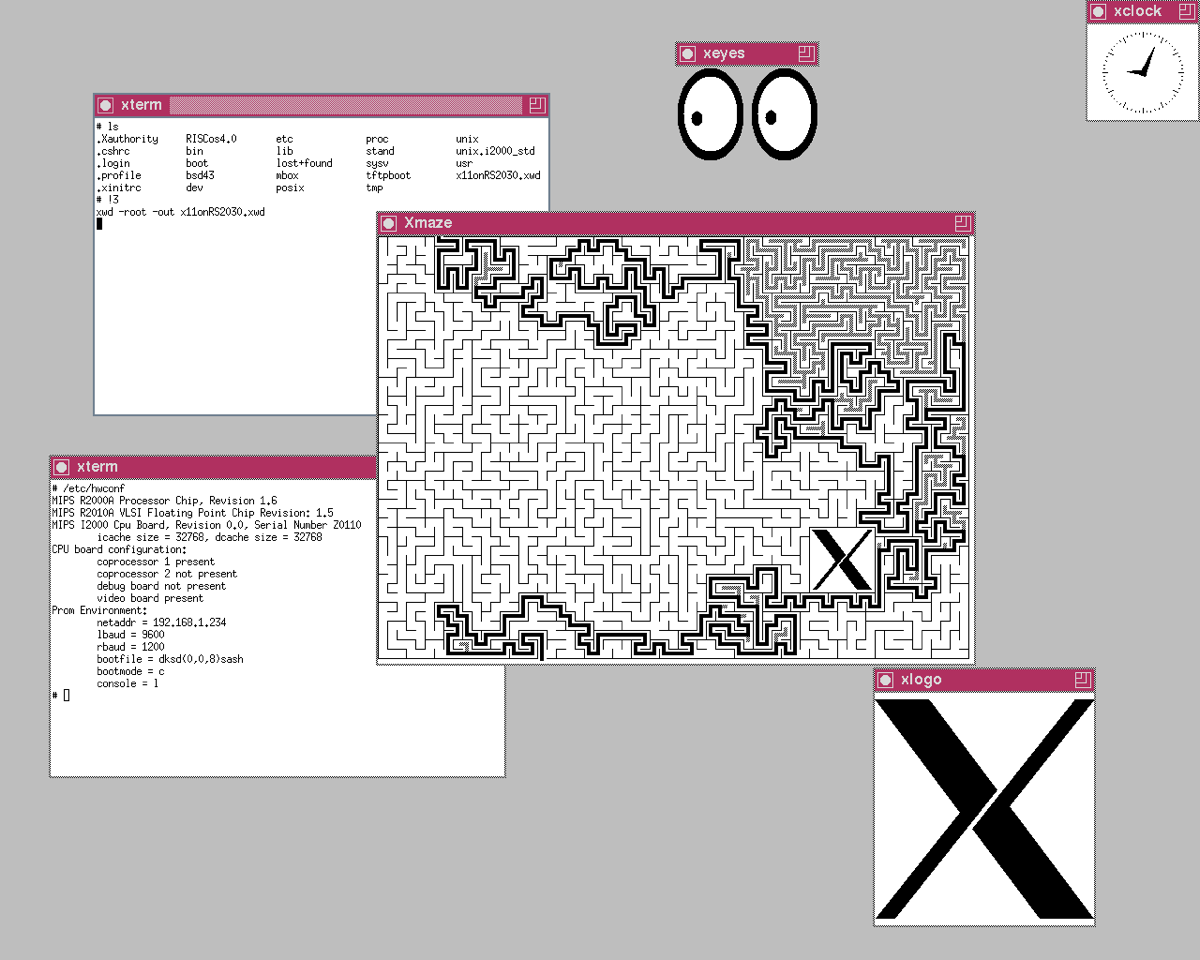

The X marks the spot!

Hey, we have a mighty frame-buffer, made for 1280x1024x8 pixels, so what’s more natural than running X-Window?!

MIPS actually sold “RISCWindows” separately for mucho $$$. It was an “optimized” X11R4… well, while the frame-buffer (i.e. no acceleration) isn’t anything special I really wonder what had been optimized?

Time for “real men™”, let’s install X11! And just because we can, we pick X11R5 because it fits the time around 1992. Around then I did the same for a SPARCStation 1… memoriiiiiiiies.

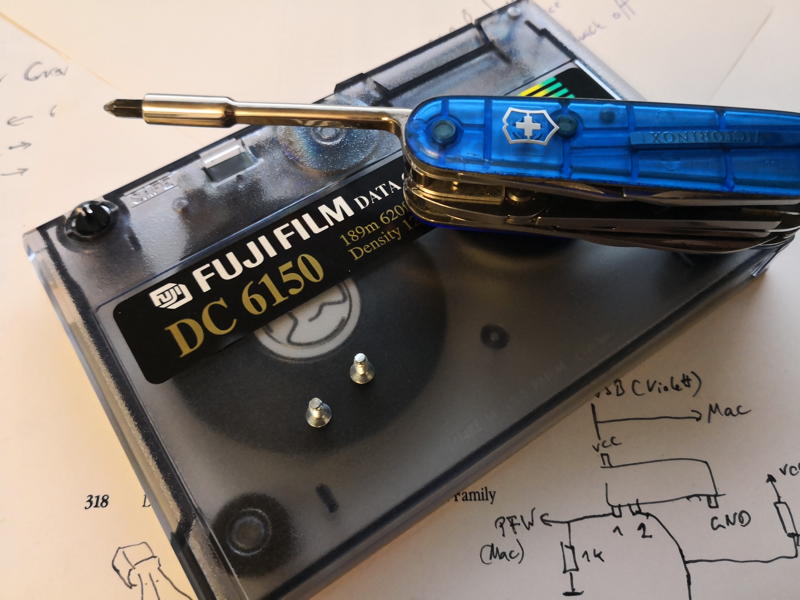

So I downloaded the X11R5 sources and very soon some new behaviors kicked in. A 16MHz machine is not the fastest kid on the block. Combined with the RS2030 lame I/O performance file decompression is a drag. So it’s actually much faster to copy an uncompressed tarball over the slow 10mbps line than having a smaller file transferred quickly and then let the 2030 chew on it forever (ah, and there’s no gzip out of the box – you’d have to gunzip & compress it on another machine before).

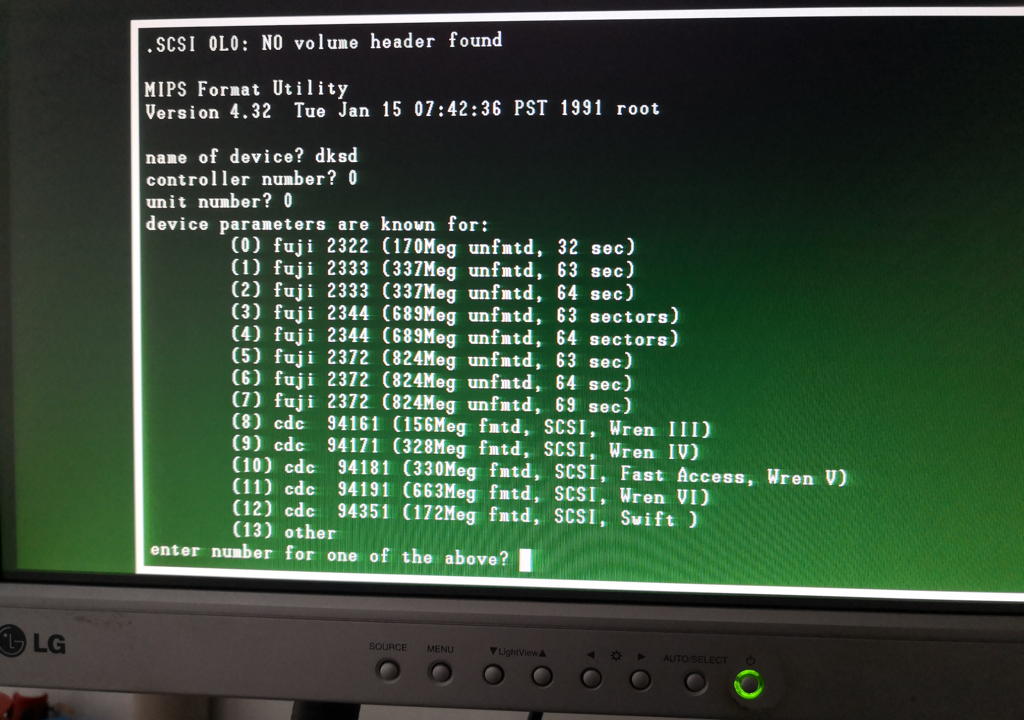

After the 200MB were moved over I was delighted to find a mips.cf config file being part of the source. Let’s have a check:

make World BOOTSTRAPCFLAGS="Mips" >& world.log

gave an instant error… the crappy RISCos sh does not know about redirection of every output into one file 😐 So I had to make sure it’s using csh… and while were at it: You have to switch the system to BSD mode (vs. System V). This can be done by putting /usr/bsd43/bin into your $PATH before anything else.

Traps and hints

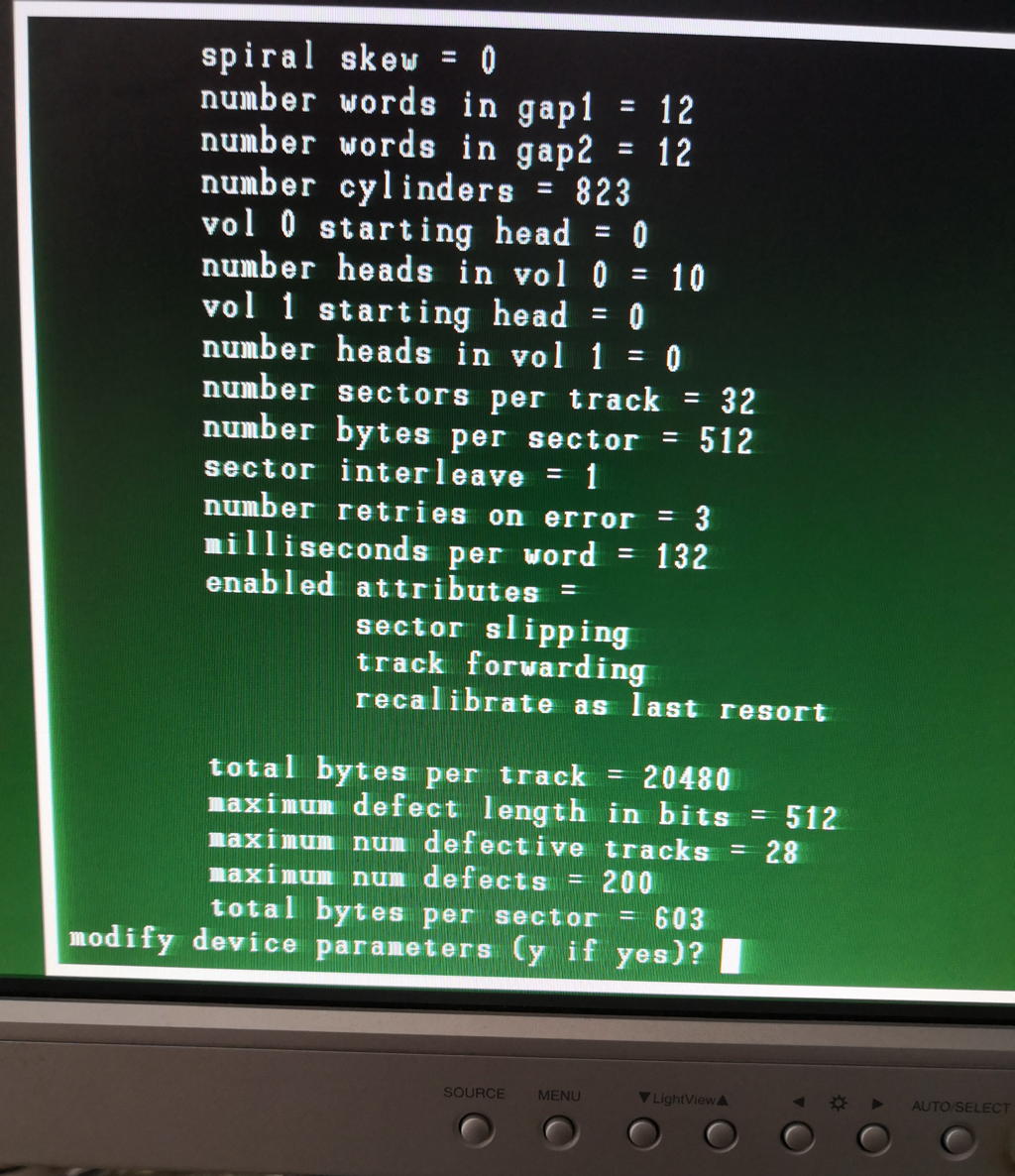

Many makes later I wondered why make always remade all objects. Reading Imakefile and many Makefiles did not light a bulb. Then there it was –facepalm– all source-files hat a creation date of 2018 because I unzipped and compress‘ed them on my Mac. And while the tools and libs on RISCos aren’t Y2k aware, the filesystem sure is. Doh!

Memo to myself: Touch all source files once before running make! Remember, we’re in 1999 on this system. This is important because a full make of X11R5 takes 6hrs on the RS2030!

Every now and then the Mips cc barfed on some code. From old newsgroup posts I learned that nobody were able to compile R5 out-of-the-box. And nobody who managed it was kind enough to post their changes. So I had to reinvent the wheel…

During this journey I stumbled across a more recent “graphics driver” source from MIPS (ddx in X11-lingo) which I incorporated into the sources – and fixed the bugs which it introduced…

One day (and night) later, the black screen of my RS2030 flickered into white, then grey and… taadaa:

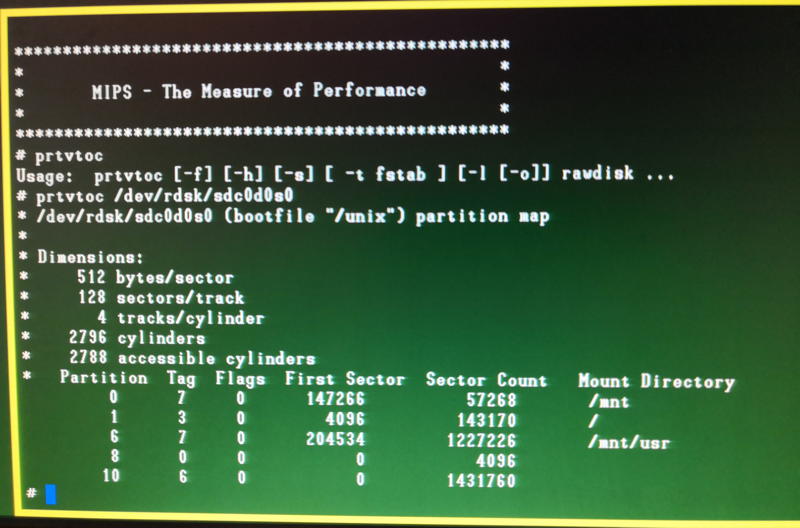

X11R5 as vanilla as it gets, runing the classic twm window-manager. The lower xterm shows hwconf, the grandfather of IRIX’ hinv.

Currently I’m fighting with fvwm – this would be a good window-manager given it’s about the same size as twm but much more versatile.

My complete X11R5 build is available as tarball here – 90MB, ~300MB decompressed. Better have a big hard-drive 😉

Un-tar to/usr/src, make sure your date is set beyond that of the files in the archive. The archive is ‘un-cleaned’, i.e. all binaries and objects are still there. This way you can just call make install to install this build onto your system – or make adjustments to sources without having to wait half a day for the compile run to finish.

Again, you will need a RISCos 4.5x system – it does not make any sense on any other system than a MIPS box!

Make yourself even more comfortable

Many years of Linux and other grown-up UNICES make using RISCos very…. tedious. The standard shell is IMHO a serious pain… the supplied csh makes life better but still, it could be better.

So here’s a (growing) archive of tools I was able to compile or dig out somewhere in the depths of the web. As soon as I got gcc working reliably this archive should grow faster providing more improvements:

- Mosaic (2.4 & 2.7b4)

- amd

- color_ls

- elm

- fvwm (2.0.42 – prebuilt for RISCWindows, does not run with “my” X11R5 compile)

- gcc.2.7.2 & lib

- htadm

- htimage

- httpd

- in.cfingerd

- in.pop3d

- libfpvm3

- libgpvm3

- libpvm3

- lsof

- make (3.75)

- nslookup

- perl (5.004b)

- pgp

- pvm

- pvm_gstat

- pvmd3

- pvmgs

- sendmail (8.9.0)

- ssh (etc. see the archive README)

- wu-ftpd (2.4)

- xpm (3.4g)

You can download the above mentioned binaries as tarball over here. Please mind, they’re totally useless if you don’t have a MIPS RISCos 4.x machine.

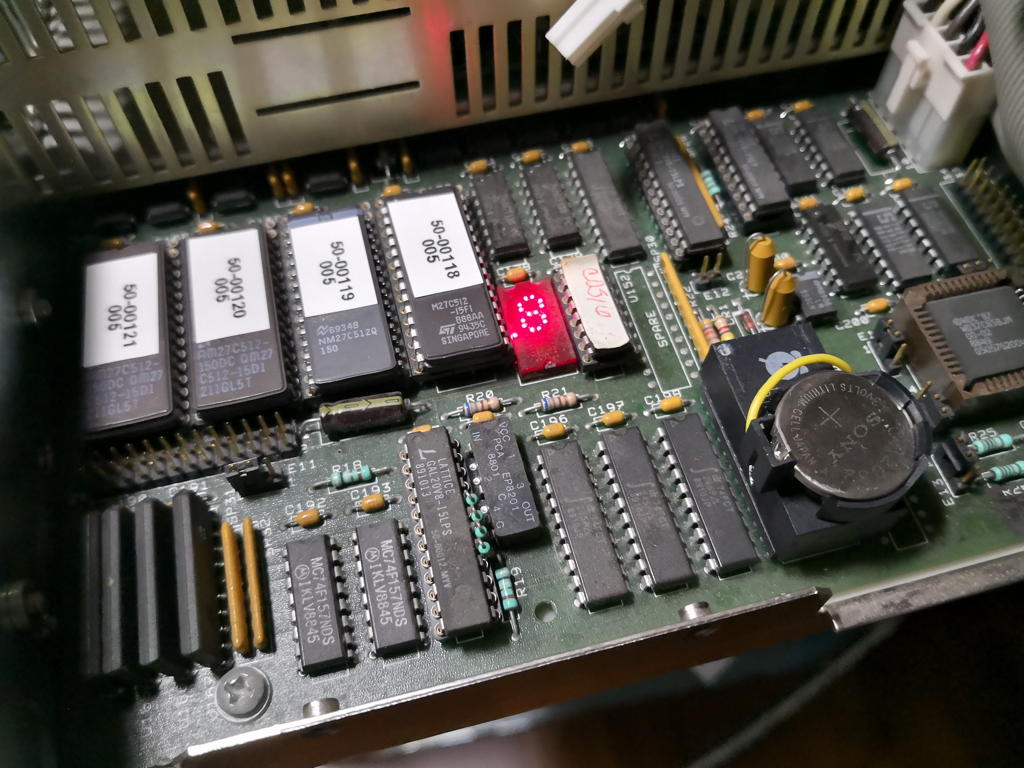

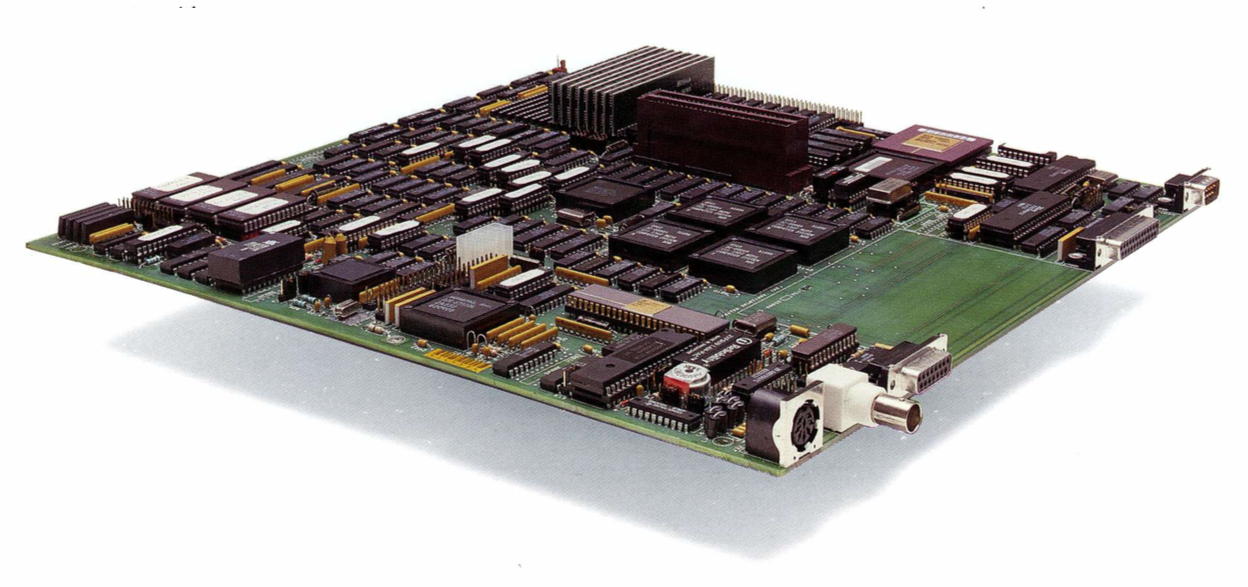

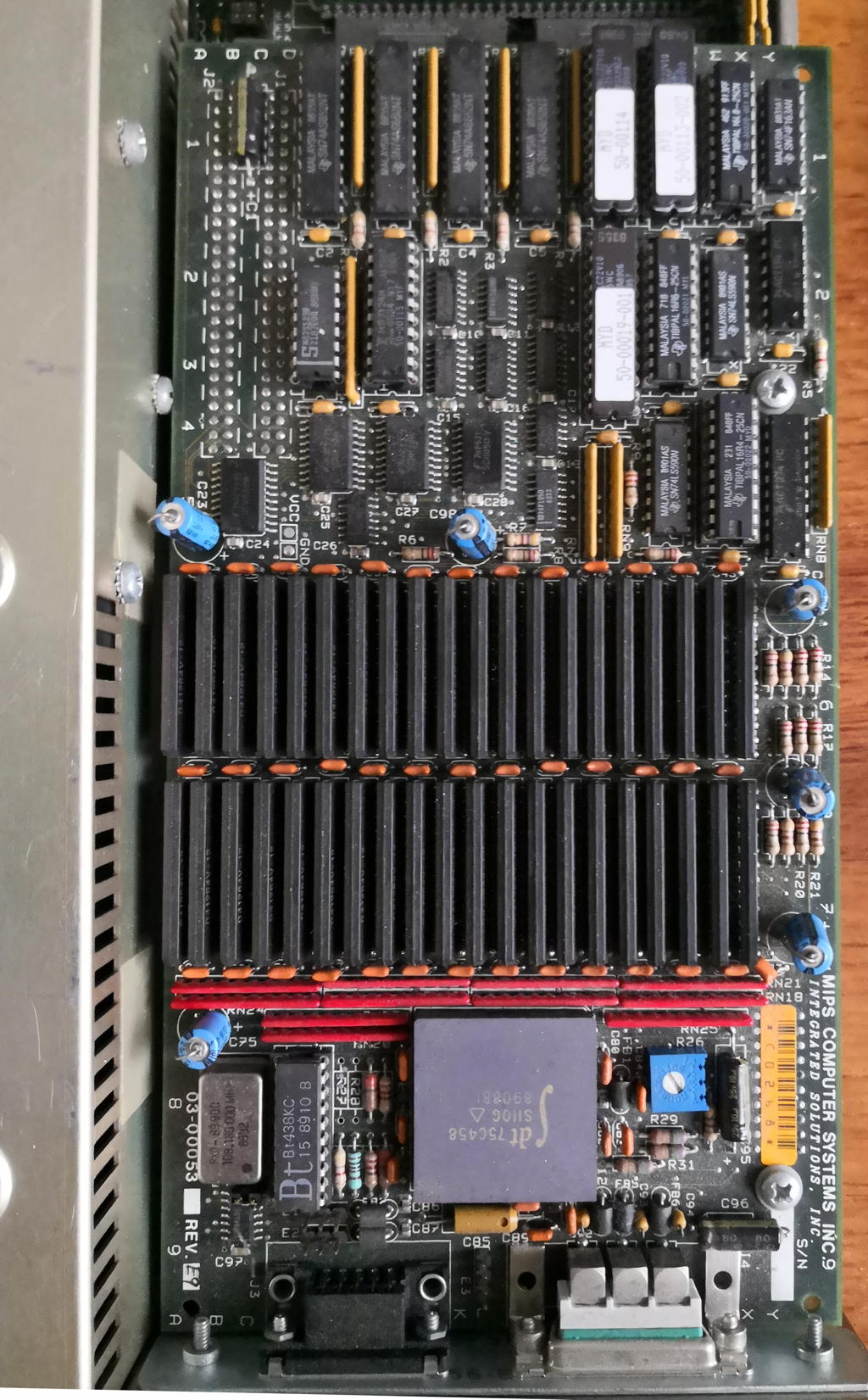

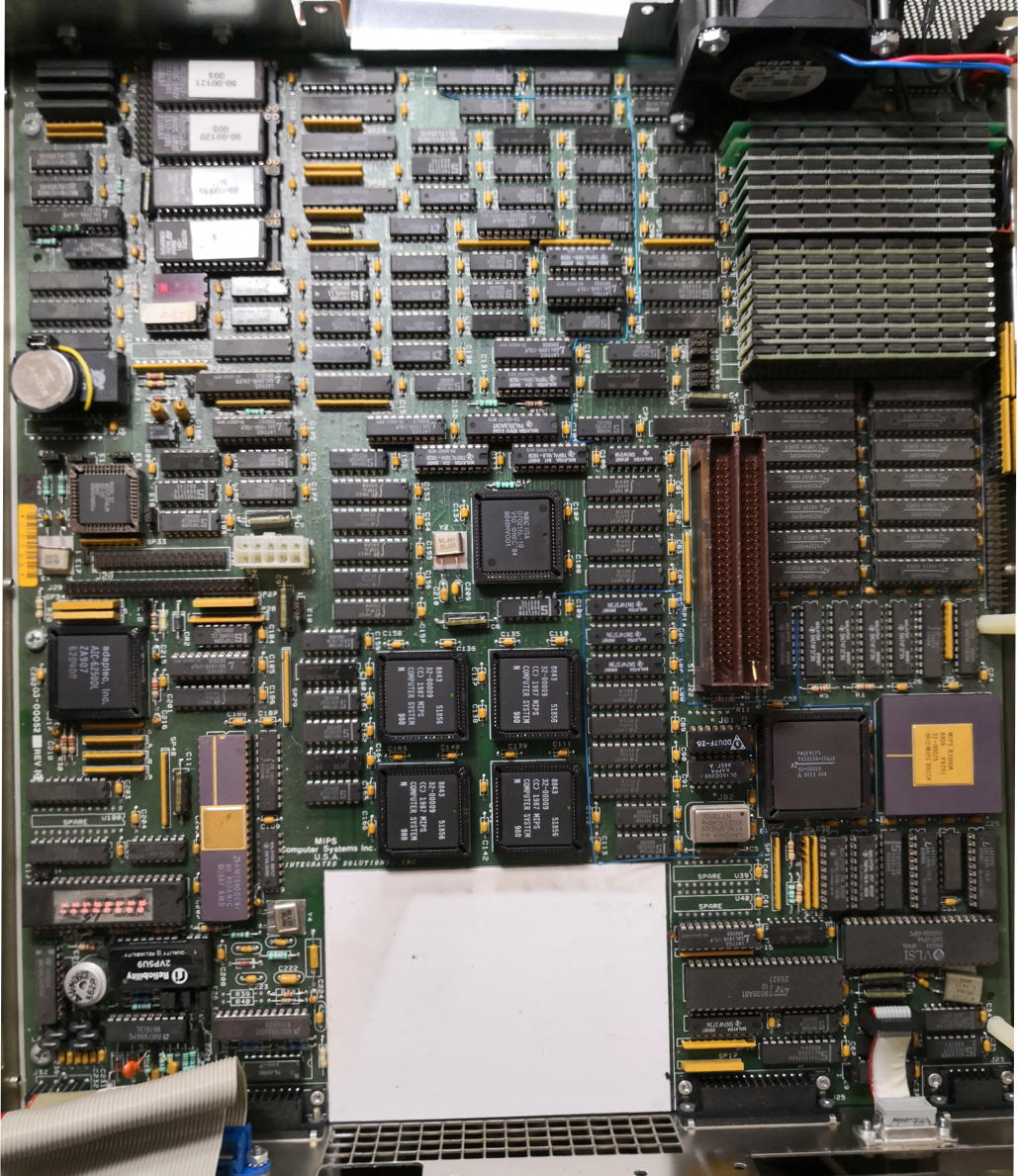

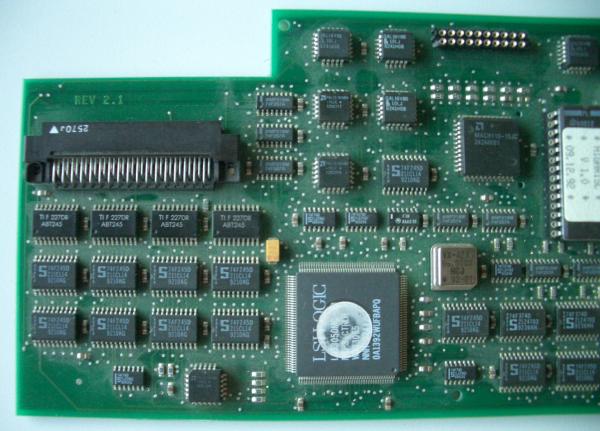

Hardware mods

There’s not much to mod here – especially given that replacement parts are hard to get in case something went wrong.

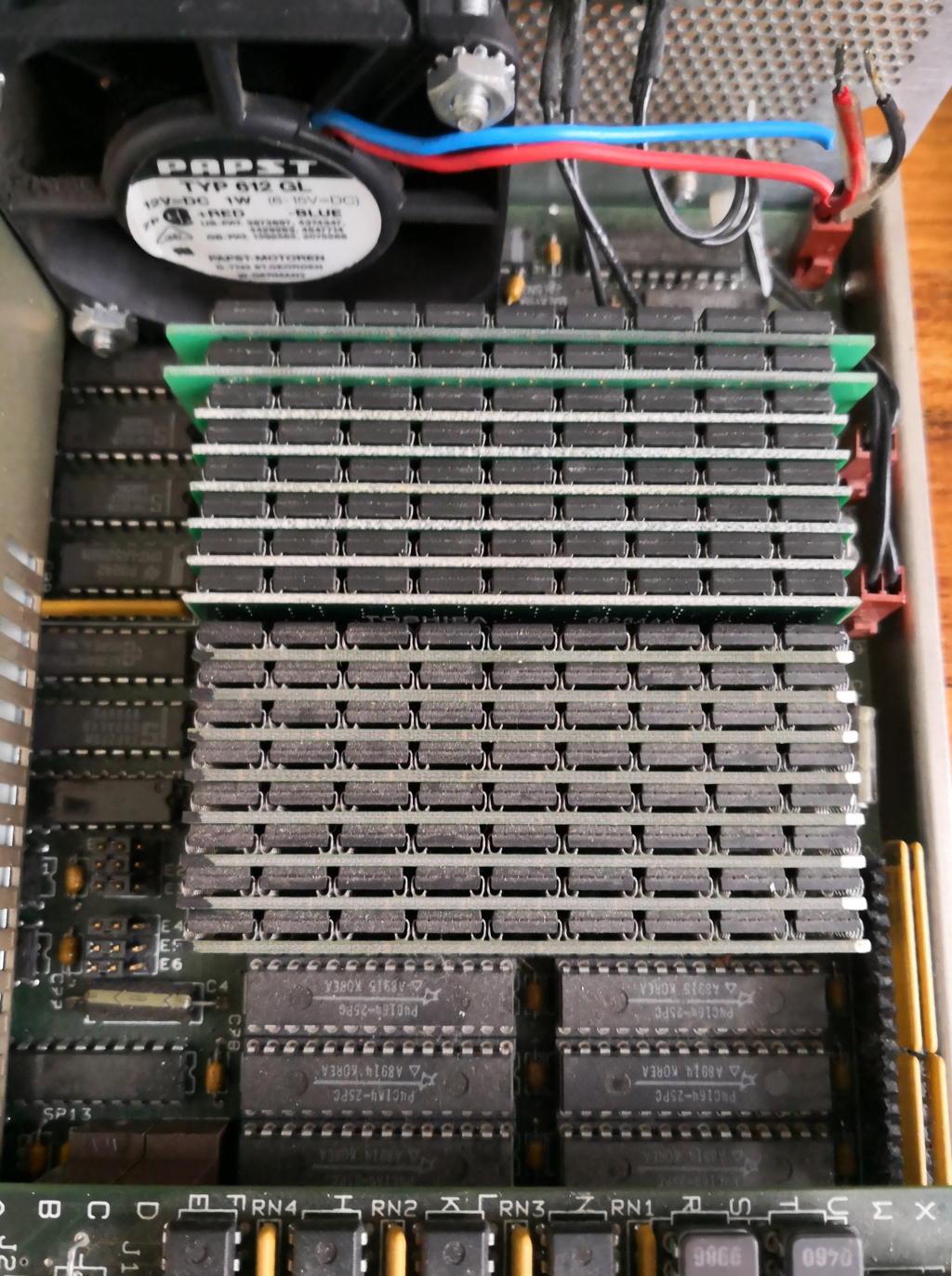

I tried to replace the very loud fan inside the power supply. But this did not work out as well as it did e.g. with my Sun Blade 150.

This is mainly due to the fact that this single fan not only cools the PSU but the whole system and thus needs quite some static-pressure which simply can’t delivered by standard PC fans.

If interested, read more about cooling vintage workstations in this post.