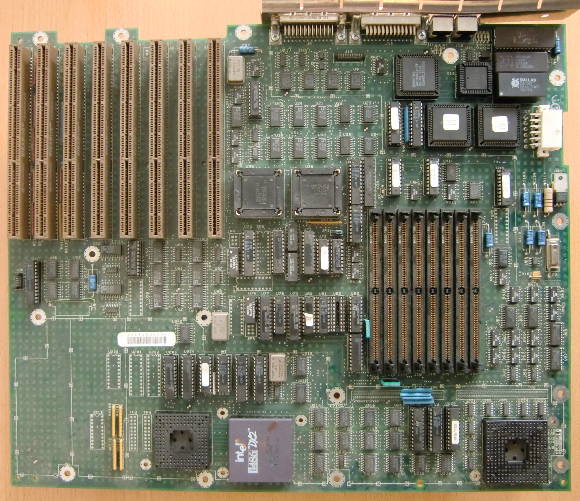

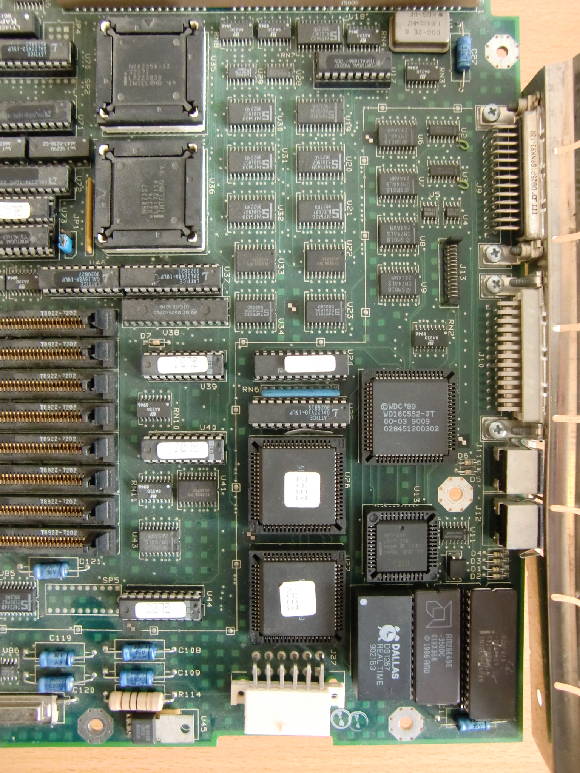

Years ago I got that broken Olivetti CP486 board (the predecessor of the LSX 5010 and 5020 family) – one of the two ever made i486/i860 combo Mainboards (the other one was the 4860 by Hauppauge). Well because it was broken, missing important parts and I felt like I’m the only one on the planet having such system I dumped it.

There’s life out there!

Now I learned there are at least two LSX 5010 owners left on this planet and one of them contacted me, primarily asking for an i860… well, long story short:

His LSX 5010 was broken, too, but complete! We agreed on a deal: I try to fix it (plus an i860) and he’ll give me a system out of his collection.

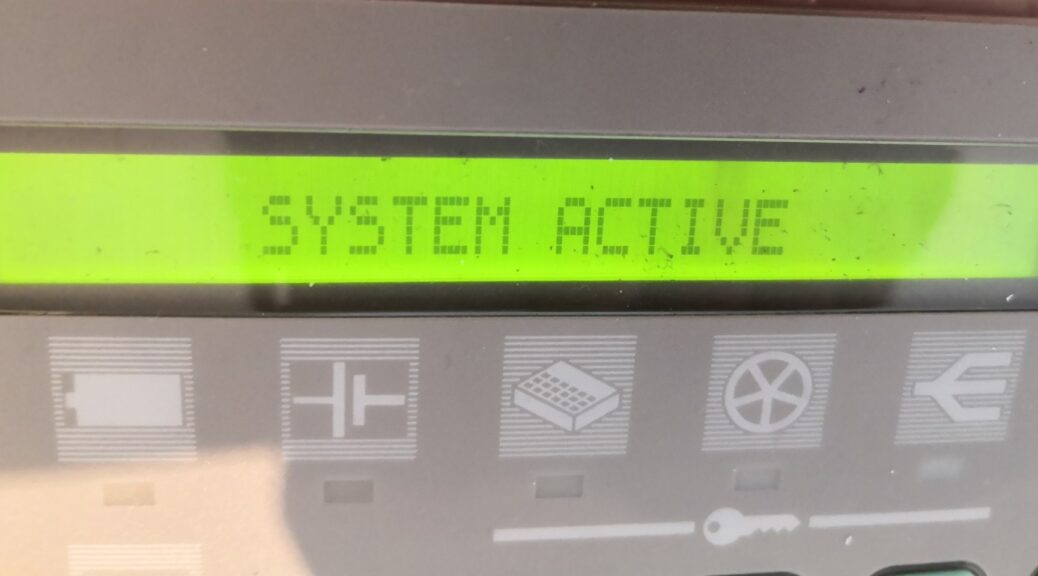

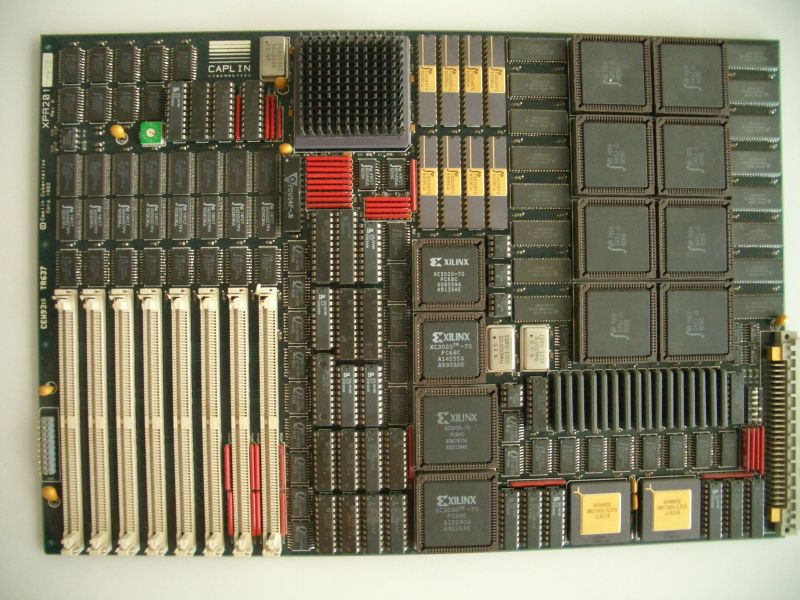

Some days later I had everything I’d call a good-to-go system:

The grey box with an LCD display is the “console”, giving you POST information, a speaker and some buttons. Next to it the huge power-supply and in the slots you can spot the EVC-1 graphics card an my trusty ISA/PCI POST card…

Let there be light

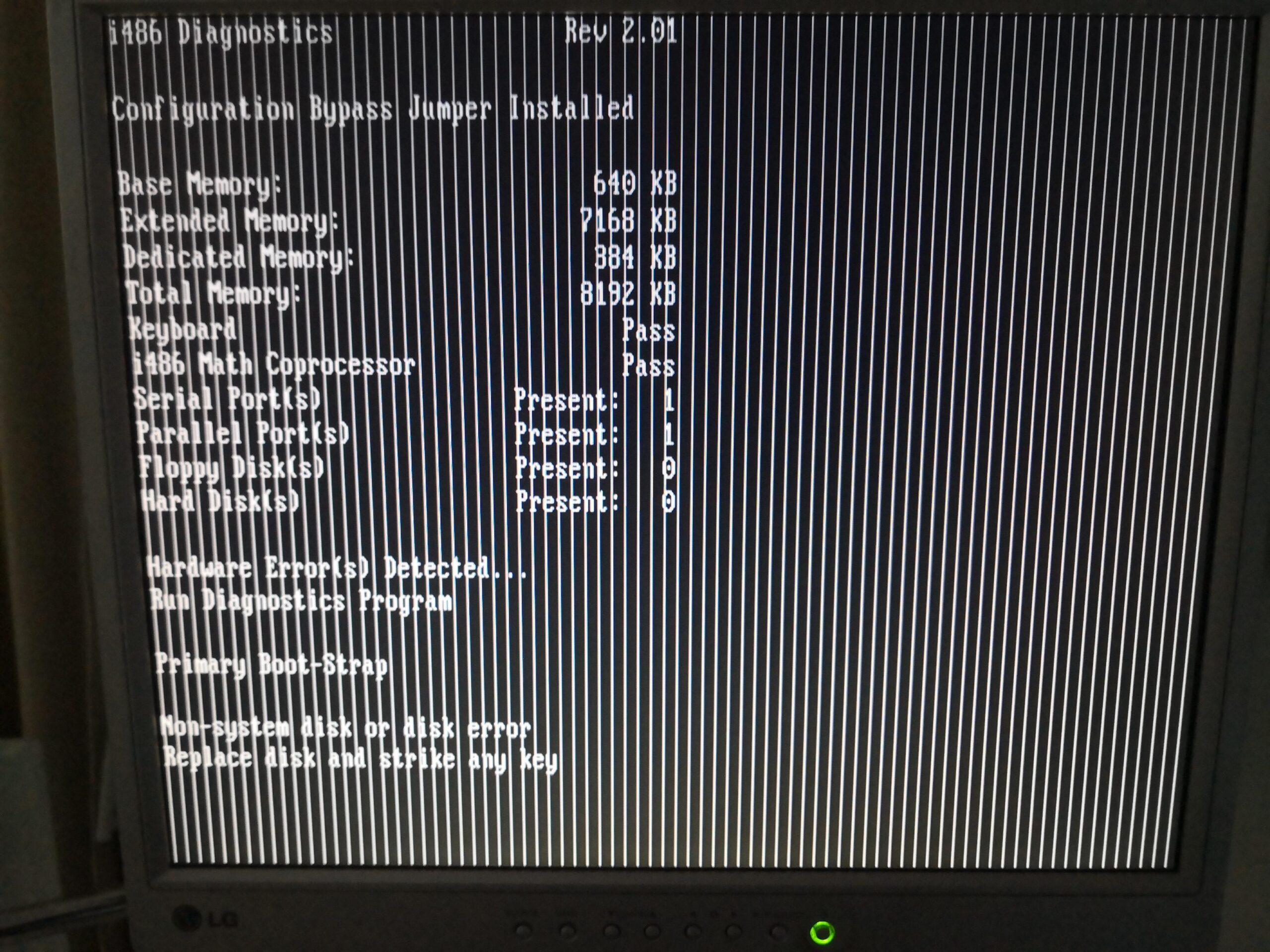

Booting the system just the console showed a “CMOS Periodic Int Error“. Doing a warm-boot it replaced by a „Base 128k Ram Error“.

Additionally it behaved somehow flaky, booting into different states every now and then:

These three Errors were solvable:

- Flaky behavior: Replacing all caps – this always helps. Believe me. The system booted into a reproducible state after this.

- CMOS error: The dreaded DALLAS CMOS clock-chip… we all know the drill. Its battery is empty and EISA systems heavily rely on a working CMOS storage. So it got an external battery surgery.

- RAM error: That was a bit tricky. The LSX’es need parity RAM. One SIMM per bank. Max. mem is 16MB – I only have 16MB+ SIMMs. So I had to get small parity PS/2 SIMMs. 2x4MB did it.

Booting the system now, the console greeted me with

- „Console Passed“

- „P.O.D. Running“ (That’s the Power On Diagnostic)

…and then „Non-Maskable Int. Error“. Dammit! This can have many reasons, most of the time it’s RAM (parity). But in my case, it’s been different…

That was a fun one (actually two):

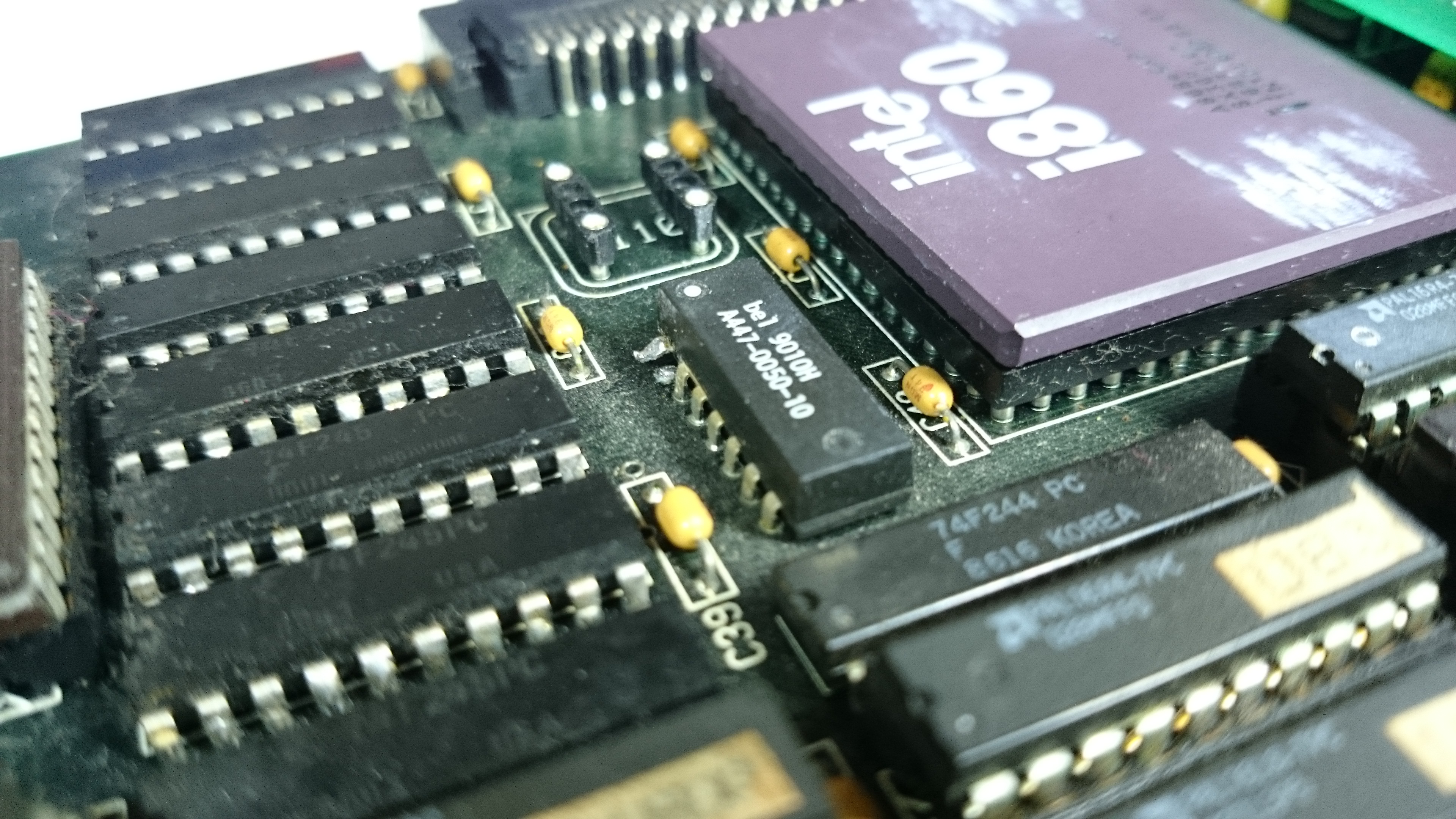

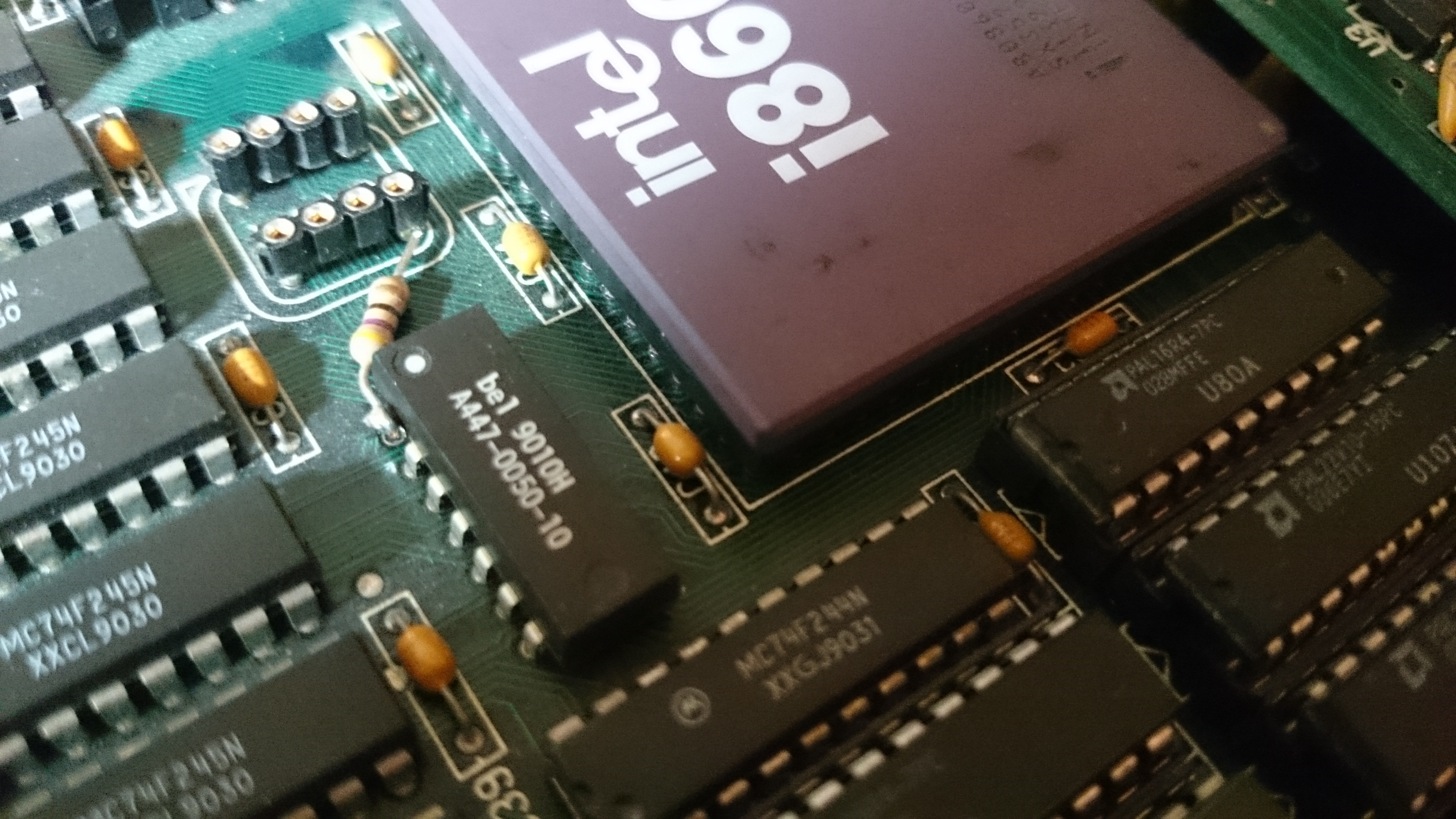

The trace to the i486 processor NMI-pin (B15) was scratched and needed repairs. But it still kept throwing that error. Why-oh-why?!?! After a whole day of digging I had a severe facepalm-moment:

The owner replaced the CPU by an 80486SX because he was under the assumption the LSX 5010 was an SX system. But it wasn’t. It’s a 80486DX @ 25Mhz system (while the 5020 is 33MHz).

And while everybody is claiming the SX is just a DX minus FPU… it is not a 100% drop-in replacement!

While the DX’es have their NMI-pin at B15 the SXes have it located at A15 (where DXes have IGNEE) and B15 is not-connected. Doh! (Checkout the pinout here)

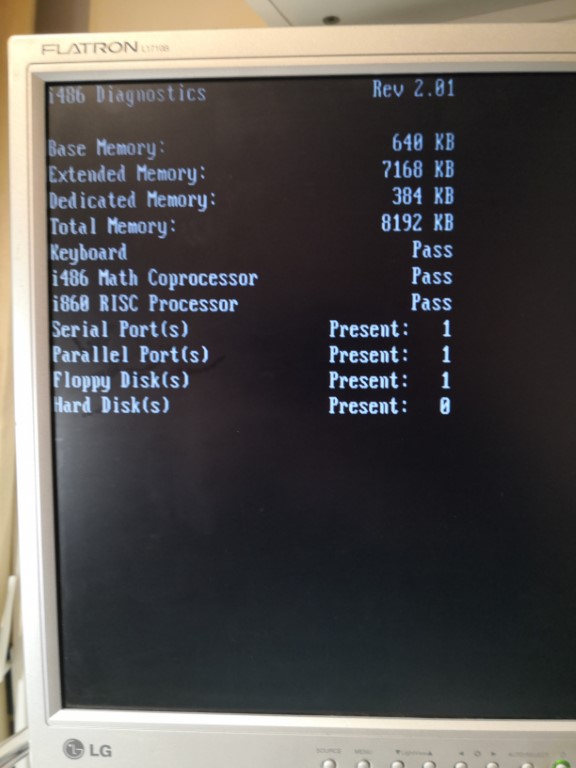

So replacing the SX by one of my 486DX we finally got a full boot! Tadaa:

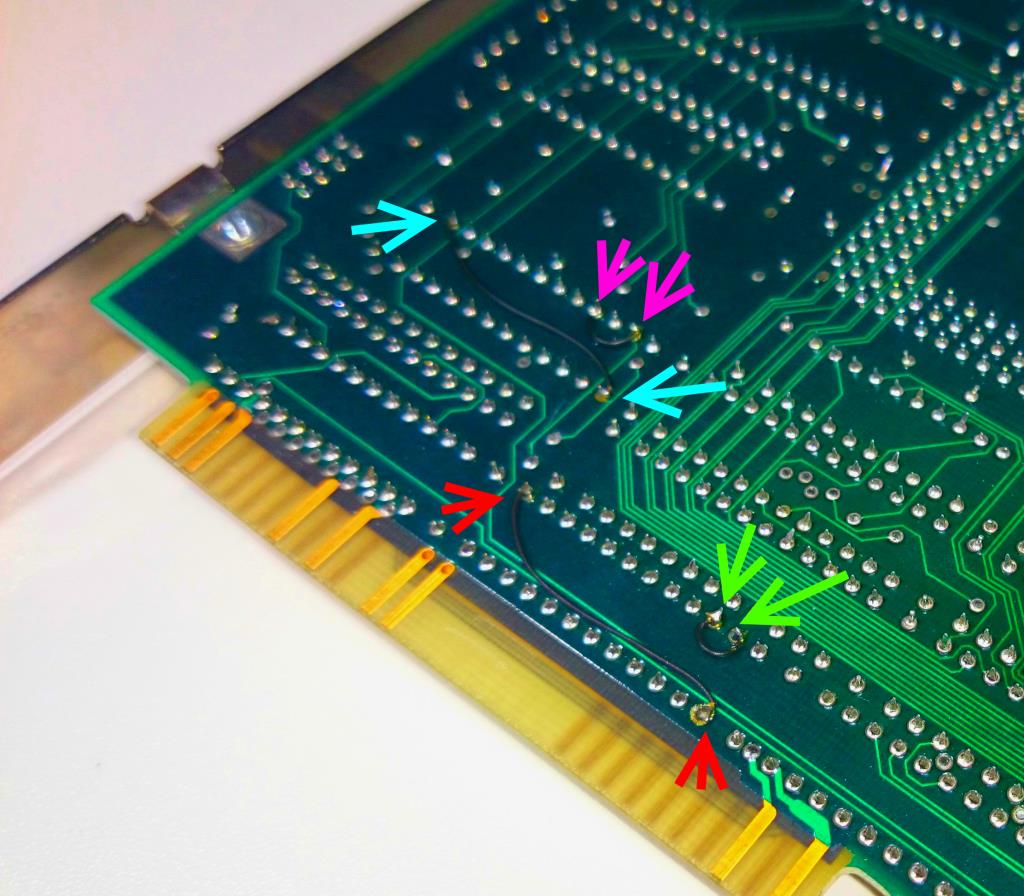

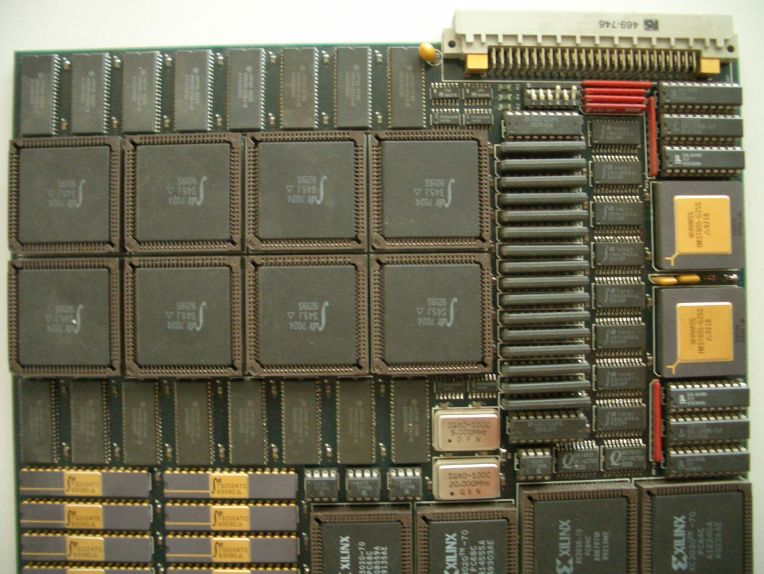

Those stripes came from the EVC-1, which definitely also had its problems. So checking its board with my microscope I came about this:

Uhhh…. a cracked diode (D14) connected to address-line A0 to the video RAM. That explains the lines quite well.

When the new DA5 (BAR43S) diodes arrived I replaced the broken one, fired up the LSX 5010:

Looking good, booting into the EISA CMOS setup and while editing the config I could watch the picture disintegrating by every keystroke. More and more garbage was displayed, columns disappearing until it was all black.

The EVC-1 literally died in action in front of my eyes 🙁

I’m not sure what happened here. The fixed address-line can’t be responsible for this. All ICs still get their clean 5 volts. I suspect that one or more of the many old PALs (some of them even bipolar) died…

Ride on…

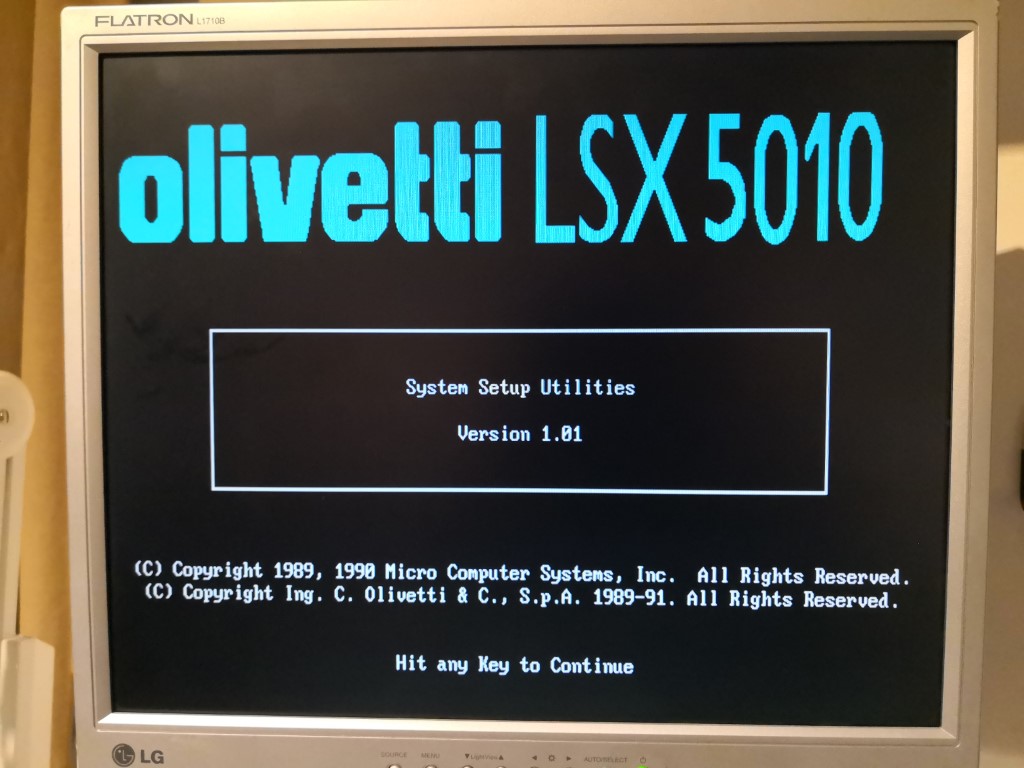

Anyhow, plugging in my ET4000 workhorse I was able to resume the setup. EISA systems always need a setup tool to tell them all the features of their Mainboard as well as the cards being installed. Luckily the owner had the basic tools at hand… you’re screwed without them.

So this is the one for the LSX booting:

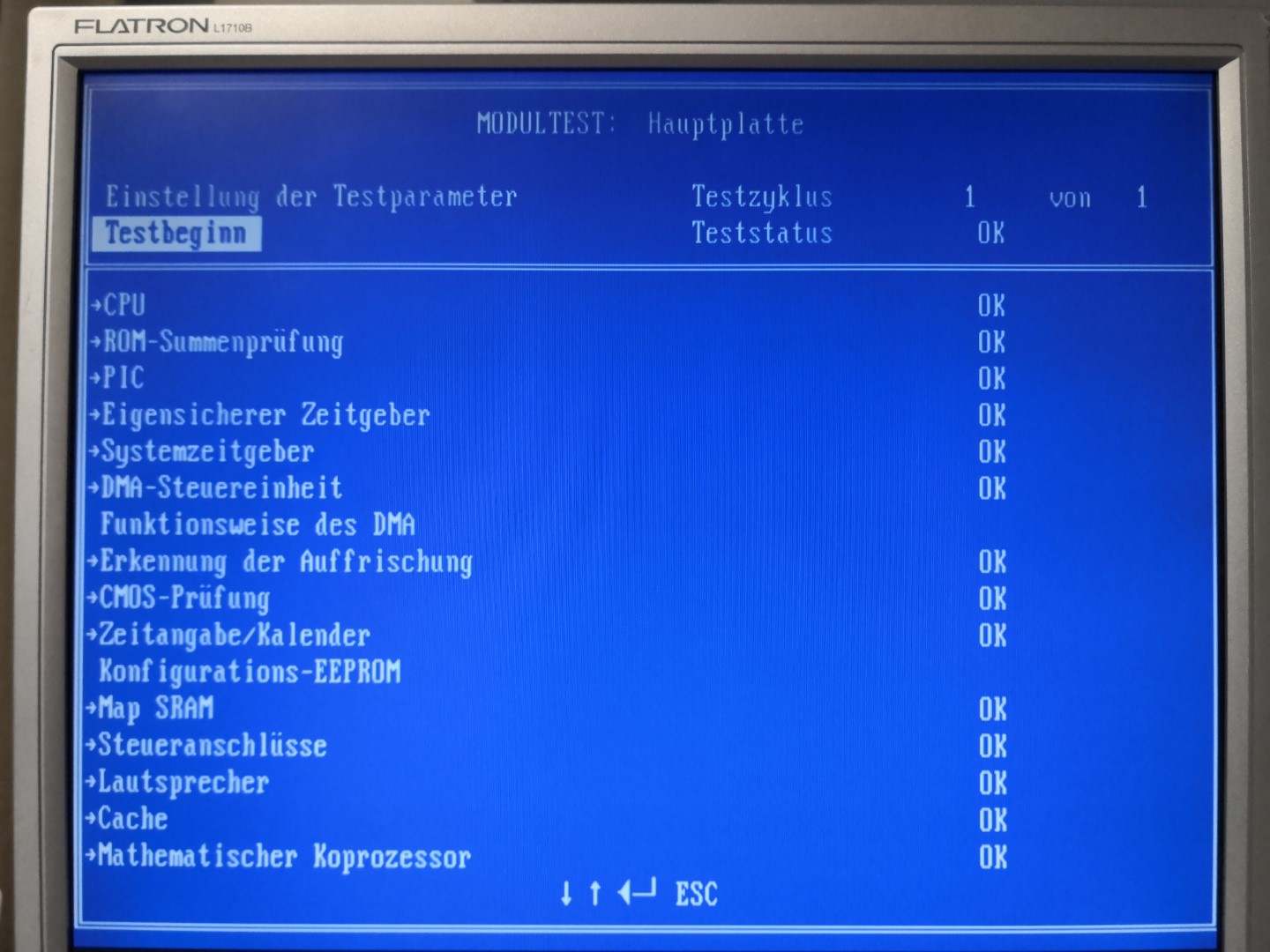

After that’s been done I ran the diagnostic tool – in German just for the fun of it (You can spot all those “OKs”, right?)

But wait a second! Isn’t there something missing?

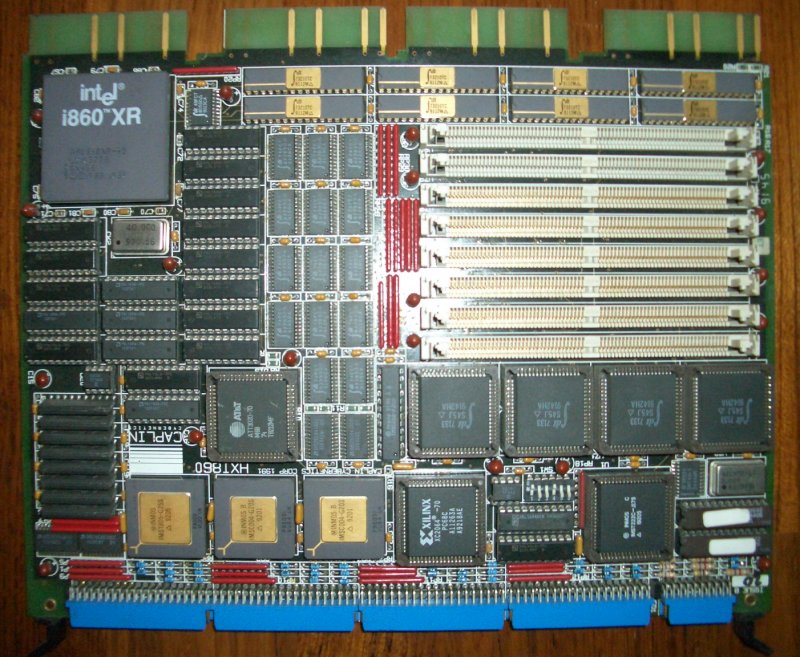

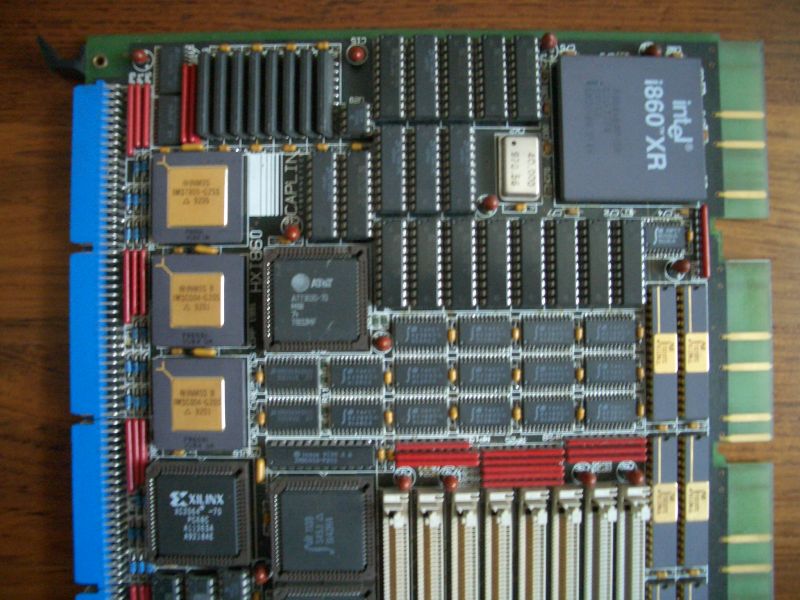

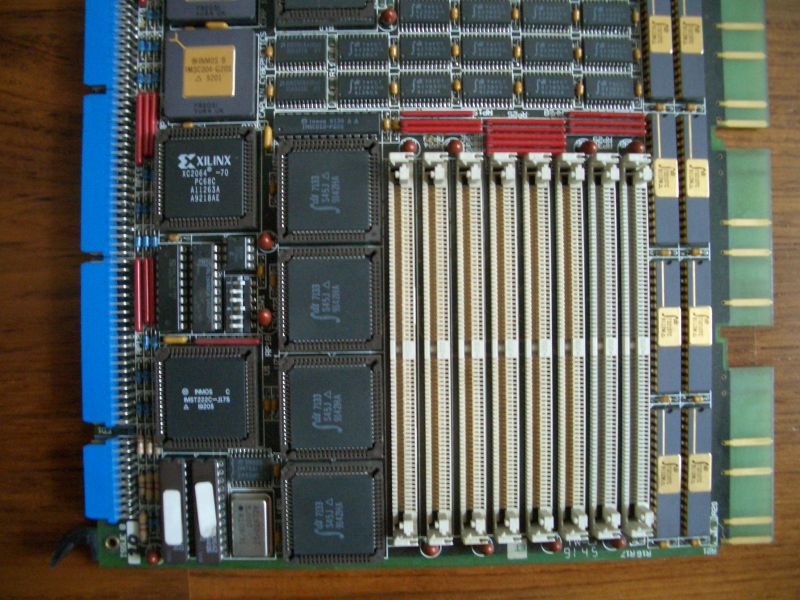

You’re right… here you go:

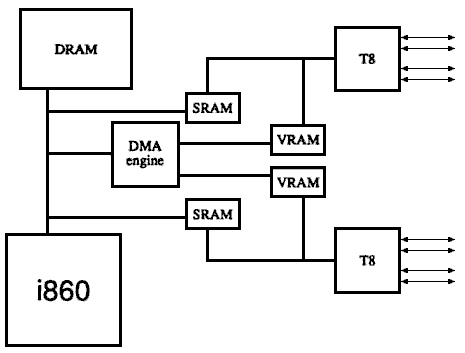

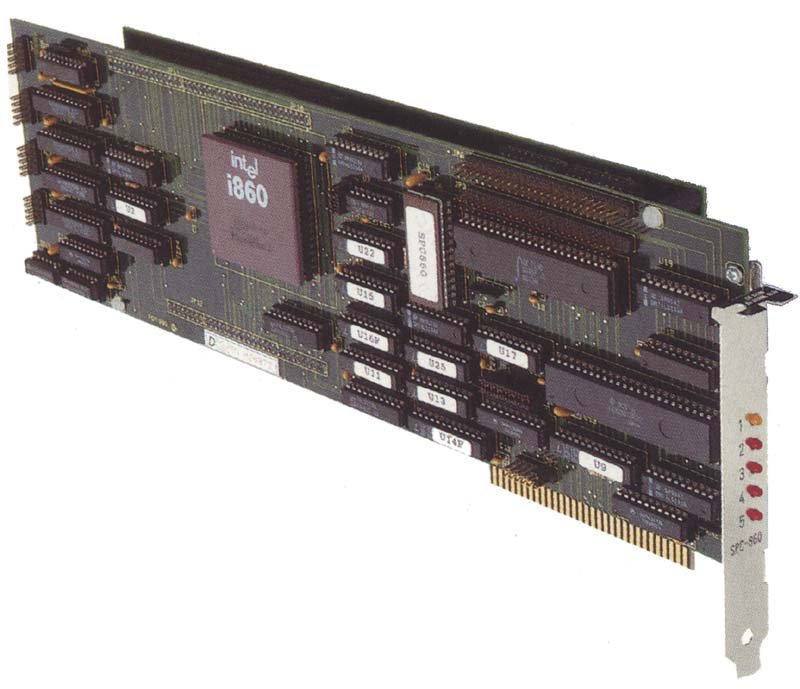

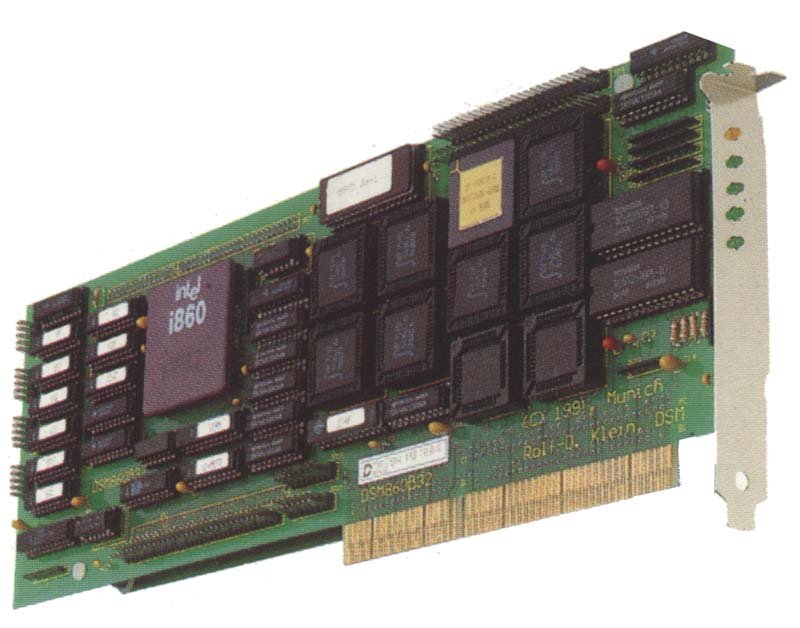

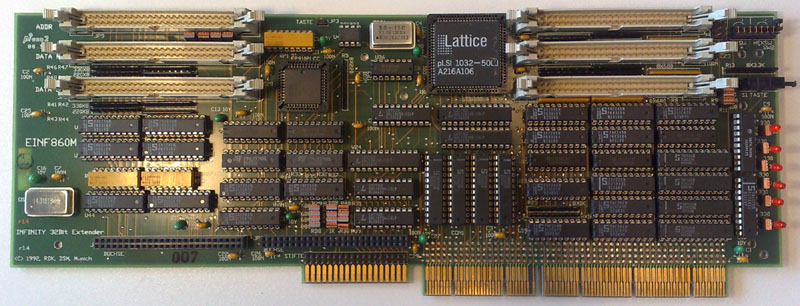

The mighty i860 RISC processor… and it is detected just fine: “Pass” 🙂

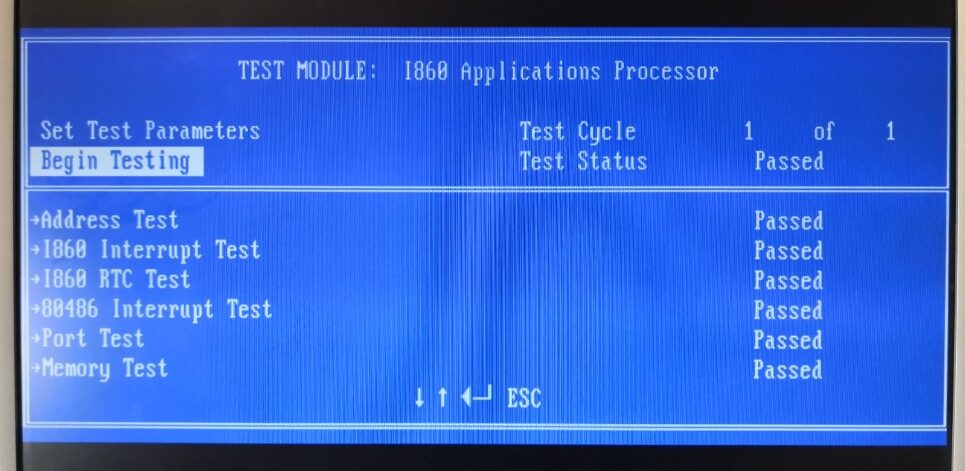

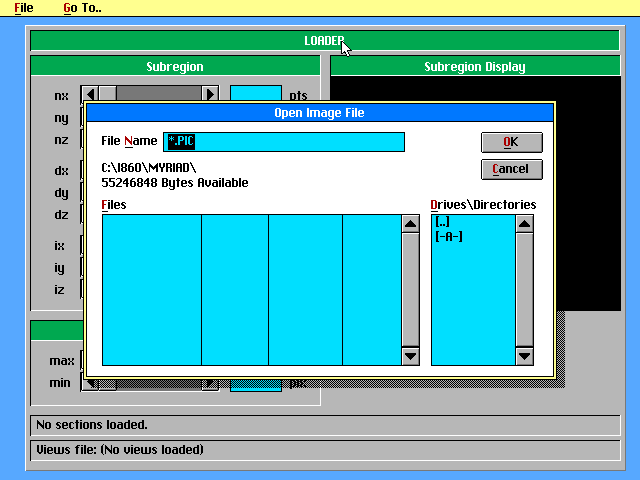

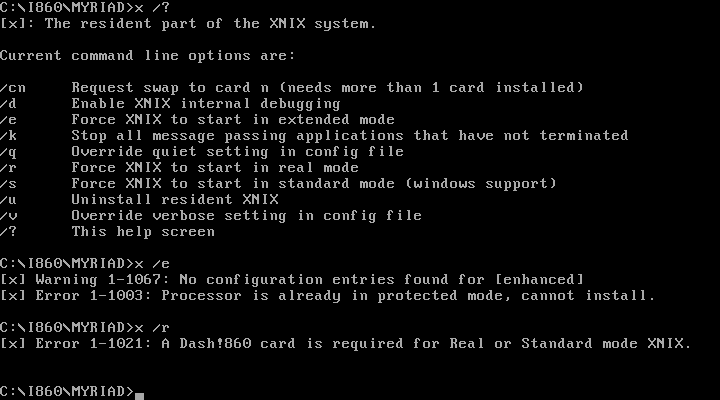

But does it work, too?

Yes it does! Hooray… mission accomplished!

Downloads

As usual, here are the dumps of the BIOS, Config EPROM and CMOS.

Additionally, you’ll find the floppy images of the config- and diagnostic tools in this archive.

Conclusion

The LSX 5010 is very much like the Hauppauge 4860 a fragile system to work with.

If the unusual configuration of EISA systems weren’t enough, the use of the many, many, many proprietary ICs (i.e. GALs and PALs) make them prone to aging and hard to fix.

They were bespoke designs, limited in their compatibility – Olivetti lists about 30 cards (VGA, SCSI, most of them multi-RS232) officially working – and most importantly need specific parts like the console and software.

Without the proper EISA config tool you always get at least error messages. Without drivers for the i860 you will not be able to use that and it’s just a heating-element inside your computers case.

Those (server) systems were meant to run as-is. Pretty much like a SUN, HP or SGI server of the same period. You can pick from like 2-3 devices to add and that’s pretty much it. They were not designed as an average PeeCee running Doom.