Well, because I’ve been asked every now and then… I’ll briefly touch the “Post-Transputer era” of Parsytec and thier PPC products in this Post.

No, I don’t own any of those, and they only run/ran Parsytecs very own PARIX OS, so I’m not of much help when it comes to revive your system. As often said, I don’t like to see Transputers being degraded to communication processors. So this is just for completeness and might help to identify your brand new dumpster-dive finding:

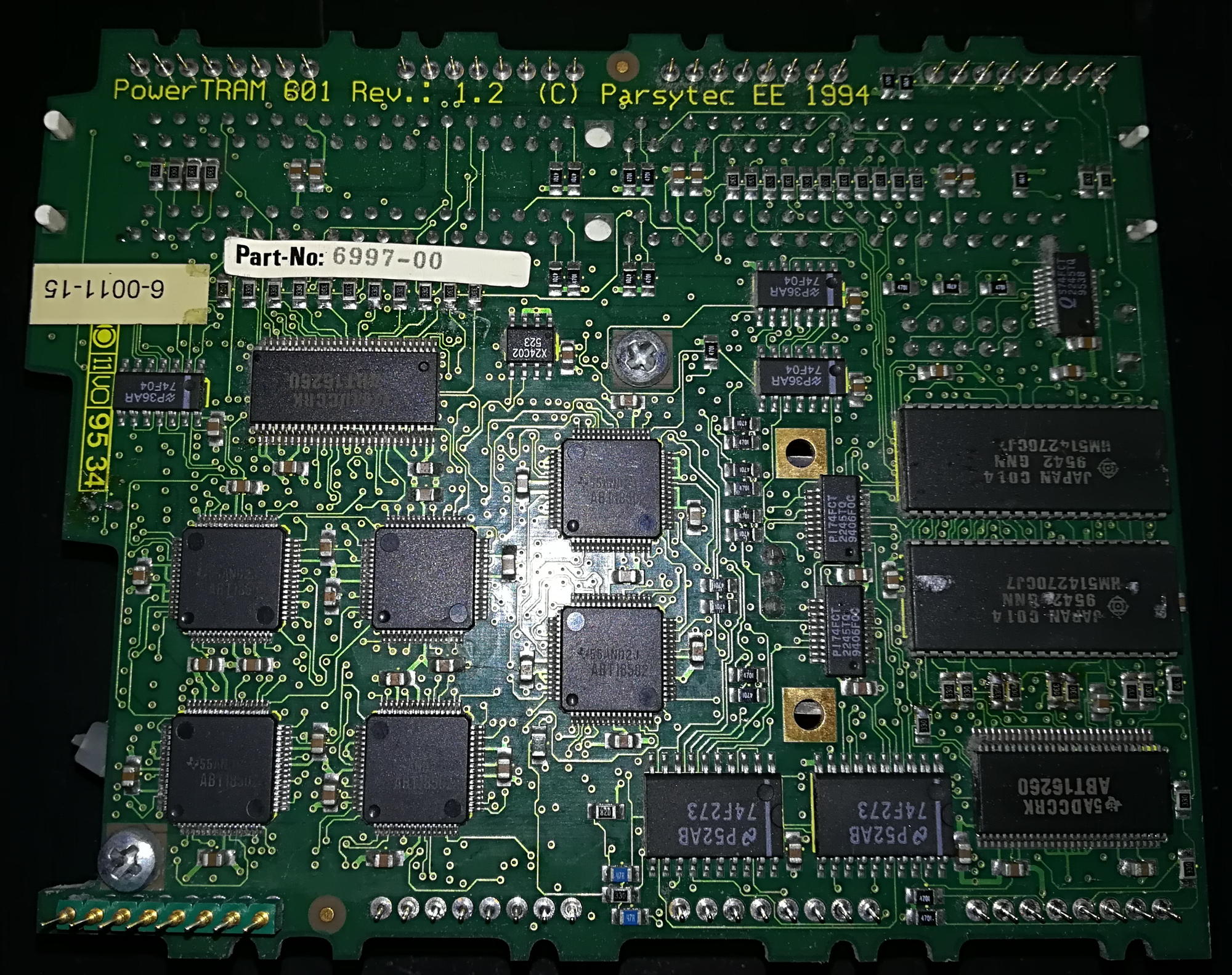

The missing link: PowerTRAM 601

These are the only Parsytec products which truly and directly bridge ‘old-world tech’ (i.e. INMOS) with ‘new-world tech’.

The PowerTRAM – available from 1994 to ca. 1996 – was a size-4 TRAM featuring an 80MHz 601 PowerPC which is memory-mapped into a 25Mhz T425 memory.

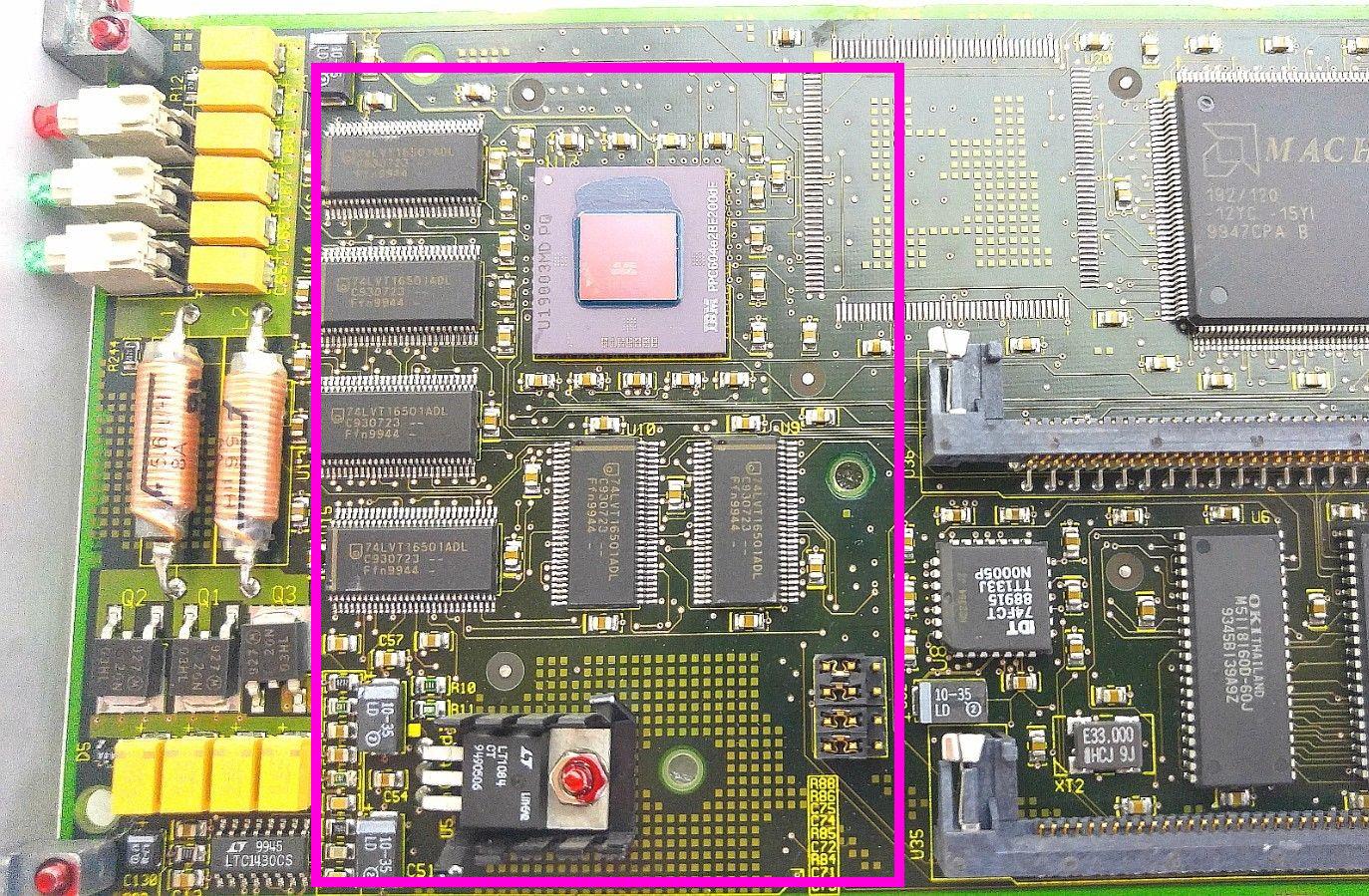

The Front has all the glamour. In the lower left corner you can spot the T425 in a QFP package, above it is a MACH FPGA most likely containing the glue logic.

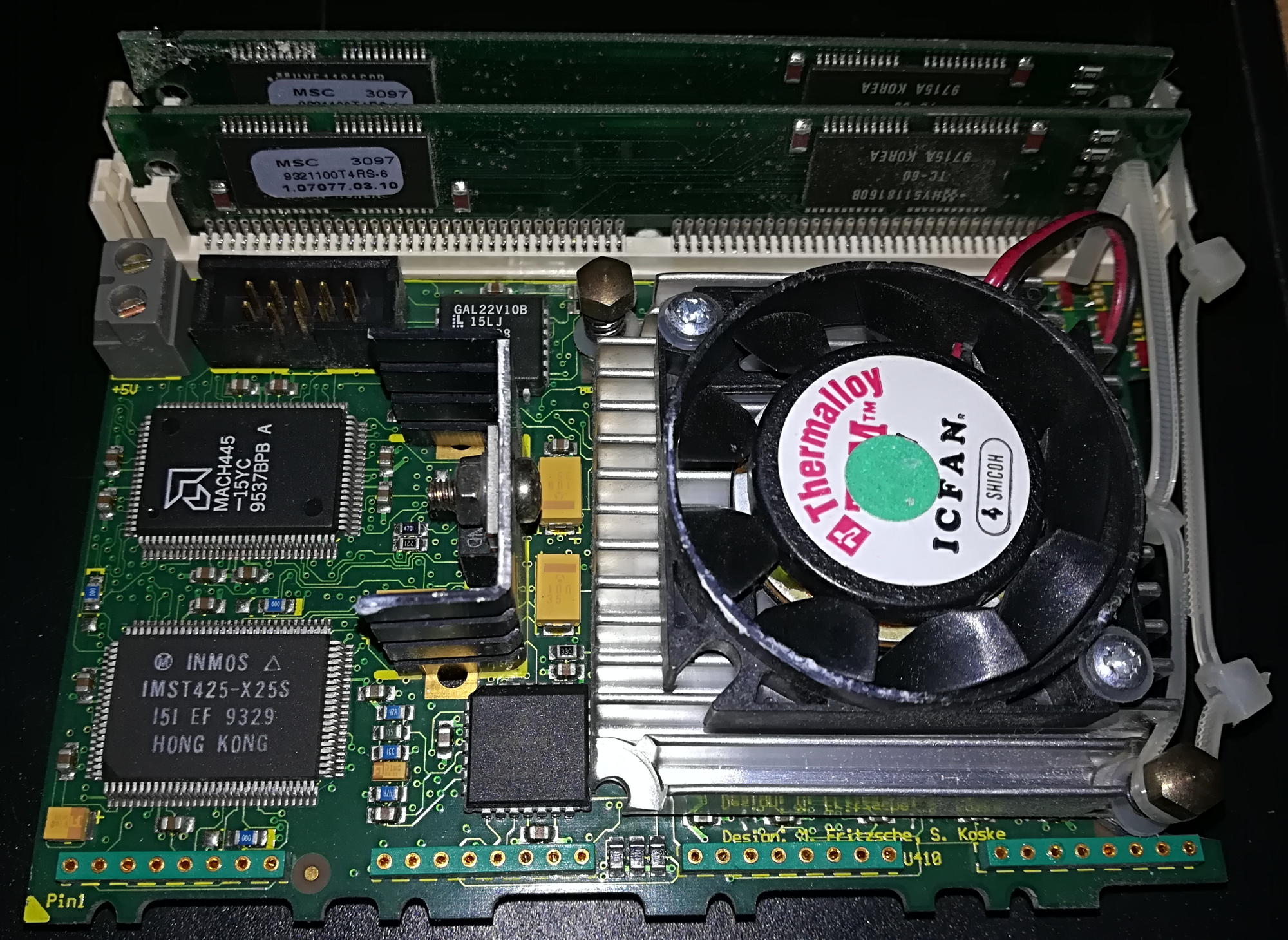

The remaining space is used by the mighty PPC601 hidden under a huge heat-sink and a fan (the 80MHz version was the fastest 601 fabricated using a 0.6 µm CMOS process and ran quite hot) as well as two PS/2 SIMM slots for its RAM.

[Pictures courtesy by J. Snowdon]

The rightmost third of backside is populated with 1MB of RAM for the Transputer and the classic logic to connect it (mainly latches).

The left two thirds are used up by quite some transceivers. Namely six ABT1852 18-bit bus transceivers (the square ones) which most likely connect the Transputer and PPC busses as well as covert the latter 3.6V level to the the T425 5 volts.

The “other x’plorer”

Well, yes, there was another x’plorer in existence. As with the GC-system, Parsytec later offered the “PowerXplorer”- you may guessed it already: It used the cluster from the PPC601 powered GC systems.

Interestingly enough there seem to be 2 versions in existence. At least the German computer magazine c’t reported in May 1994 that there’s a 2 CPU and a 4 CPU PowerXplorer… and featured the two below images as a proof.

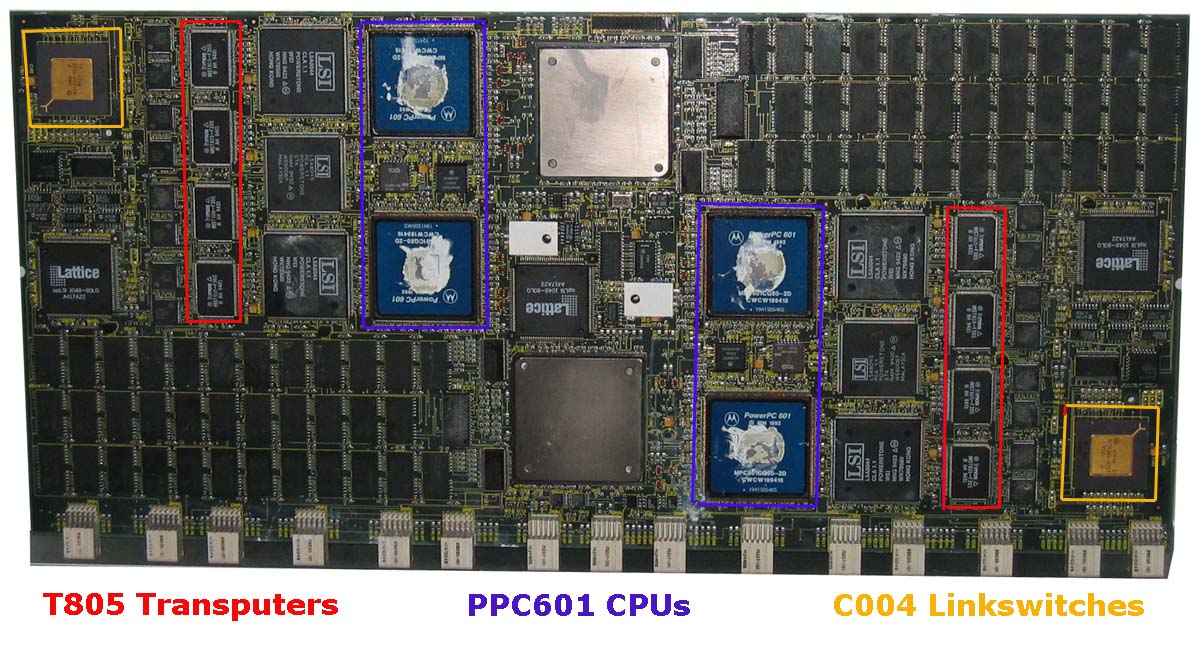

Maybe the 2-CPU model was a beta-model or even using early PPC604’s? At least it features SIMM sockets vs. the soldered RAM used in the 4 CPU version.

If you’re really-really interested in that model, here’s a big (Click to zoom) picture of the PPC cluster board. I’ve marked the important parts for easier finding.

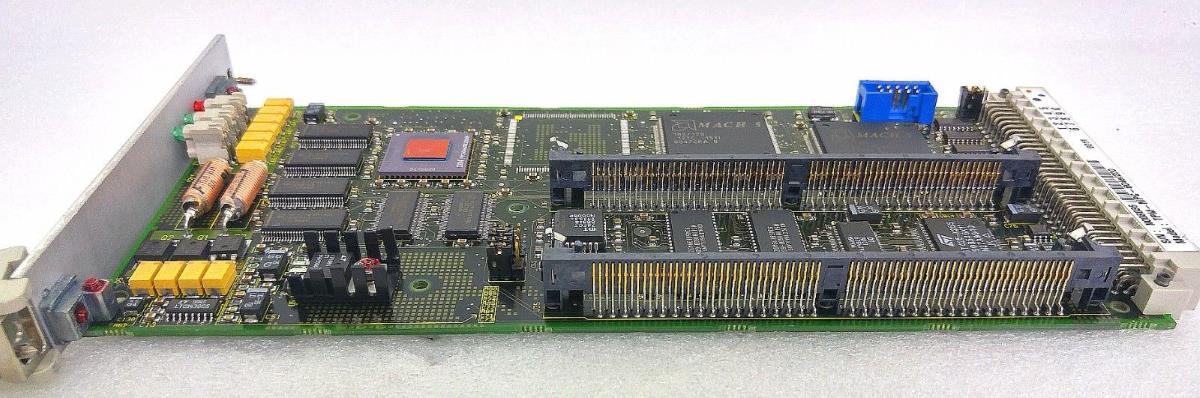

TPM-MPC

The TPM-MPC (Transputer Processing Module – Multi Processing Card) is basically a single CPU version of the PowerXplorer. So one T425 is handling the link communications and, depending on the revision, a 100, 133 or 200MHz 604e PPC is doing the number-crunching.

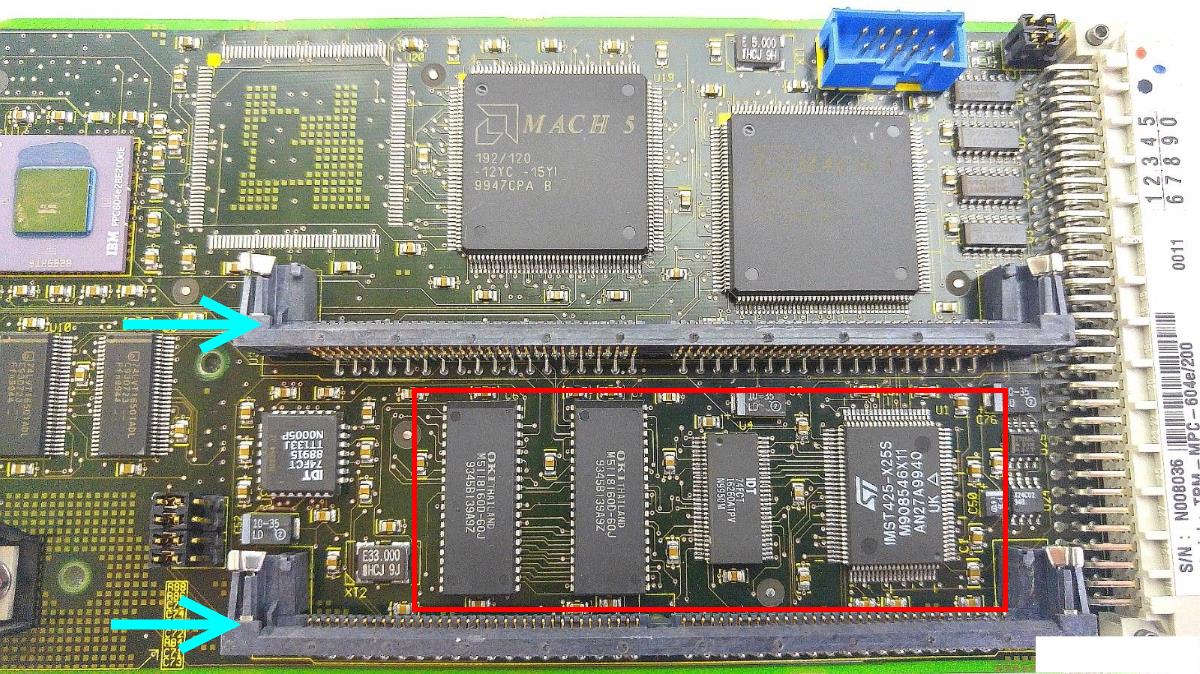

This is a Revision 1 TMP, far left in red frame you can spot a T800 Transputer with its RAM – in the green frame is the PPC604 and soldered 16MB of EDO RAM:

A somewhat different version (can’t spot a Rev making) providing 32MB RAM to a 100MHz PPC604 and having the glue-logic between the 2 CPUs shuffled around a bit compared to the previous version:

The Rev.2 model features SIMM sockets for the EDO RAM and has a slightly different layout.

The Transputer part on this one is a T425 (who needs a FPU for just doing data-shifting?!) with 1MB RAM, framed in red between the 2 SIMM sockets, marked with blue arrows:

The PPC side (heatsink removed) including some drivers and the 3.3V supply.

Independent of the revision, TPMs went into a TPM-Box. A simple, steel box with a power-supply, two fans and a backplane for 4 TPMs. This is it from the front (grille removed):

…and the even less impressive back.

As some ePay auctions mention “taken from RVSI 5700 SYSTEM” I assume the main usage for TPMs were optical analysis/inspection systems which Parsytec built when turning their backs to super-computing.