WEITEK

#### WTL 3167 FLOATING-POINT COPROCESSOR

PRELIMINARY DATA September 1988

The WEITEK WTL 3167, also known as the WEITEK ABACUS, is a high performance single-chip floatingpoint coprocessor for Intel's 80386 microprocessor. It is hardware and software compatible with the WEITEK 1167 coprocessor daughter board. Fully supported by a wide selection of application packages and by high-level language compilers, under DOS, UNIX System V.3, and XENIX System V.3, the WTL 3167 provides a superior floating-point accelerator for highend PCs, workstations, industrial robots, graphics, and numeric controllers.

| Contents                               |     |

|----------------------------------------|-----|

| Features                               | 1   |

| Description                            | 1   |

| Block Diagram                          | 2   |

| Hardware Designer's Section            | 3   |

| Software Tools Overview                | 20  |

| Applications Programmer's Section      | 21  |

| Systems Programmer's Section           | 48  |

| WTL 1167 and<br>WTL 3167 Compatibility | 54  |

| Ordering Information                   | 55  |

| Revision Summary                       | 56  |

| Documentation Request Form             | 59  |

| Sales Offices back co                  | ver |

WTL 3167 Floating-Point Coprocessor September 1988

Copyright © WEITEK Corporation 1988 All rights reserved

WEITEK Corporation 1060 East Arques Avenue Sunnyvale, California 94086 Telephone (408) 738-8400

WEITEK is a trademark of WEITEK Corporation

MS-DOS is a trademark of MicroSoft Corporation OS 386 is a trademark of AI Architects RUN386 is a trademark of Phar-Lap Software UNIX is a trademark of Bell Laboratories X-AM is a trademark of IGC

WEITEK reserves the right to make changes to these specifications at any time

Printed in the United States of America 90 89 88 6 5 4 3 2 1

#### PRELIMINARY DATA September 1988

#### Features

| SINGLE-CHIP FLOATING-POINT COPROCESSOR                                                    | IEEE FORMAT                                                                            |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Designed for use with the Intel 80386                                                     | Conforms to the IEEE standard format for floating-                                     |

| Fits a standard 121-pin socket, which is a superset of the Intel 80387 coprocessor socket | point arithmetic in both single- and double-precision<br>(ANSI/IEEE Standard 754–1985) |

| Pin-for-pin compatible with WEITEK 1167                                                   | FULL FUNCTION                                                                          |

| coprocessor board                                                                         | Add, subtract, multiply, divide, and square root                                       |

| Upward object-code-compatible from WEITEK 1167                                            | Integer-floating-point conversions                                                     |

| HIGH PERFORMANCE                                                                          | Absolute value                                                                         |

| 5.6 single-precision megawhetstones and 1.0                                               | Compare                                                                                |

| single-precision megaflops in hand-coded Linpack                                          | Transcendental functions supported by run-time                                         |

| HIGH-LEVEL LANGUAGES                                                                      | libraries                                                                              |

| Supported by C, FORTRAN, and Pascal compilers                                             | Low power CMOS                                                                         |

| under UNIX System V.3, XENIX System V.3, and                                              | Dissipates 2.0 Watts max at 25 MHz                                                     |

| MS-DOS real and protected mode                                                            | 121-pin PGA package                                                                    |

|                                                                                           |                                                                                        |

| Description                                                                               |                                                                                        |

### Description

The WTL 3167 is a high-performance single-chip floating-point coprocessor board for Intel's 80386 32-bit microprocessor. It delivers two to three times the performance of standard 32-bit numeric coprocessors. (Benchmark results are given in figure 1.)

The interface signals between the WTL 3167 and the 80386 are provided by a 121-pin socket, called the extended math coprocessor (EMC) socket, which is a superset of the 80387 socket. The WTL 3167 is pin-for-pin compatible with the WTL 1167 coprocessor daughter board.

C, FORTRAN, and Pascal compilers fully support the WTL 3167, allowing programs to be written in high-

level languages. The WTL 3167 is upward object-codecompatible with the WTL 1167 coprocessor daughter board.

This document consists of three sections: the Hardware Designer's Section, the Applications Programmer's Section, and the Systems Programmer's Section.

This data sheet is complemented by two additional documents: The WTL 3167 Hardware Designer's Guide and the WTL 1167 Software Designer's Guide. Readers familiar with the WTL 1167 Data Sheet can simply refer to the WTL 1167 and WTL 3167 Compatibility section.

| Benchmark      | Performance     |

|----------------|-----------------|

| Linpack* (SP)  | 1.36 MFLOPS     |

| Linpack* (DP)  | .60 MFLOPS      |

| Whetstone (SP) | 5.6 MWhetstones |

| Whetstone (DP) | 3.7 MWhetstones |

Figure 1. Benchmark results at 25 MHz

### **Description**, continued

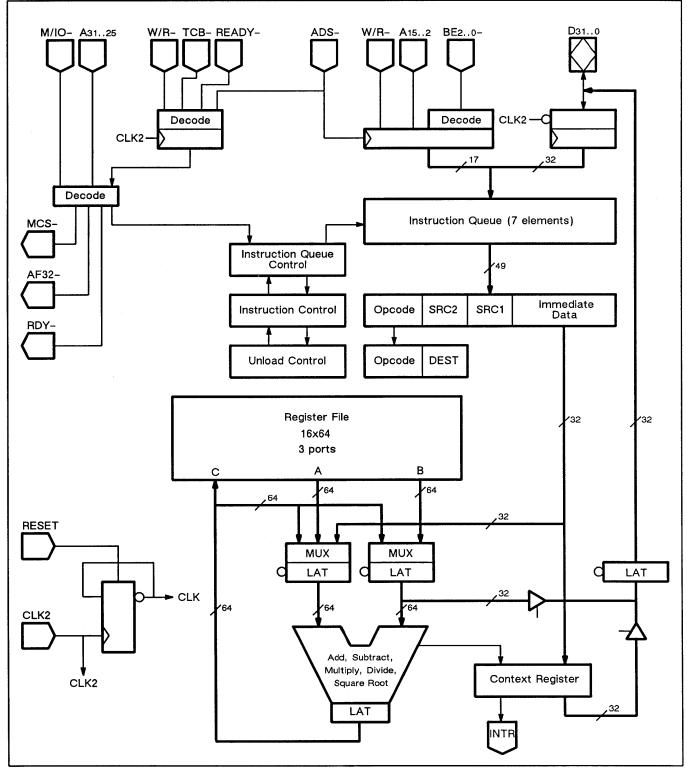

Figure 2. WTL 3167 simplified block diagram

#### PRELIMINARY DATA September 1988

### Hardware Designer's Section

This section provides the electrical and mechanical information necessary to design the WTL 3167 into an 80386 system. For more details refer to the WTL 3167 Hardware Designer's Guide.

The WTL 3167 coprocessor is a memory-mapped peripheral. From the system designers standpoint, integrating the WTL 3167 into the system is as simple as adding additional memory at an upper address. To the 80386 and its application software the WTL 3167 appears to be a segment of memory. Instructions are executed by performing memory moves to and from the coprocessor.

The WTL 3167 interface to the 80386 requires signals that are not available on the 80387 socket. WEITEK

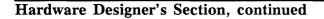

has defined a superset of the 80387 socket called the *extended math coprocessor* (EMC) socket, which is a standard 121-pin pin grid array socket. With the EMC socket, a system can make use of the 80387, the WTL 3167, or both, if one uses a small daughter board that plugs into the 121-pin socket and accommodates both coprocessors. Figure 3 shows the EMC socket pinout and size.

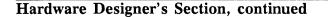

Figure 4 shows the WTL 3167 physical dimensions.

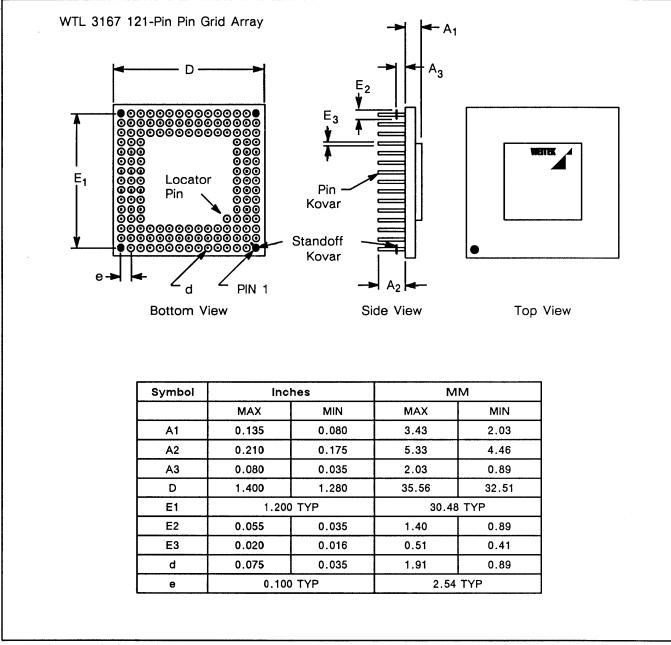

Figure 5 shows details of the WEITEK daughter board. It can accommodate both the 80387 and the WTL 3167 coprocessor.

Figure 3. EMC socket pinout and dimensions

PRELIMINARY DATA September 1988

Figure 4. WTL 3167 physical dimensions

Figure 5. WTL 3167 coprocessor board physical dimensions

#### PRELIMINARY DATA September 1988

#### Hardware Designer's Section, continued

#### CONNECTING THE EMC SOCKET

The following paragraphs describe the connection of each EMC socket pin.

#### CLOCK (CLK2)

CLK2 is the clock input to the WTL 3167. All WTL 3167 timing is relative to CLK2. This signal must be the same as CLK2 of the 80386, but the WTL 3167 should have a dedicated trace. (For more details refer to the "Clock Distribution" paragraph in the WTL 3167 Hardware Designer's Guide).

#### VDD

Five volt (+5.0 V) power supply for the WTL 3167. All VDD pins must be connected.

#### GROUND (GND)

Ground for the WTL 3167. All ground pins must be connected.

#### BUSES

Address Bus (A31..2) and (BE2..0-).

Pins A31..2 and BE2..0- should be connected directly to the 80386 address bus and byte enables respectively.

#### Data Bus (D31..0).

Pins D31..0 should be connected to the 80386 data bus.

#### 80386 INTERFACE SIGNALS

The 80386 interface signals are: Address Status (ADS-), Memory I/O Control Signal (M/IO-), Transfer Acknowledge (READY-), Reset (RESET), and Write/ Read Line (W/R-).

ADS-, M/IO- READY-, RESET, and WR- should be connected to the 80386 ADS-, M/IO-, READY-,

RESET, and W/R- respectively. Reset must be asserted synchronously with the 80386 clock to guarantee proper operation (see figure 18). In implementations using the Chips and Technologies chip set, READYshould be connected to READY- on the 82C301 and 82C302 devices, and to VCC through a 10k pullup resistor.

#### COPROCESSOR READY (RDY-)

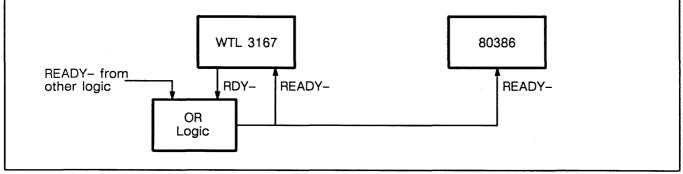

The RDY- output signal must be "ORed" into the logic generating READY- for the 80386, using only combinatorial logic (see figure 6). In implementations using Chips and Technologies chip set, RDY- should be connected to READY-.

#### MATH COPROCESSOR SELECT (MCS-)

MCS- is an output signal that is asserted when the current address is for the WTL 3167 coprocessor. It changes when the 80386 address bus changes. MCS-may be left unconnected or may be used in conjunction with W/R- to disable other 80386 data bus drivers on WTL 3167 read cycles. When pipelined addressing is used, special attention must be paid, as MCS-may be de-asserted prior to the end of a WTL 3167 read cycle, as shown in figure 17.

#### THREE CYCLE BUS (TCB-)

TCB- is an input that should be grounded in systems using the Chips and Technologies AT/386 chip set. Otherwise TCB- should be left unconnected.

#### AF32--

AF32- is an output signal used only in implementations based on Chips and Technologies' chip set. In implementations based on Chips and Technologies' AF32should be connected to VCC through a 10k resistor and to AF32- on the 82C301 and 82C302 devices. It should be left unconnected otherwise.

Figure 6. READY- and RDY- connection

#### Hardware Designer's Section, continued

#### INTERRUPT (INTR)

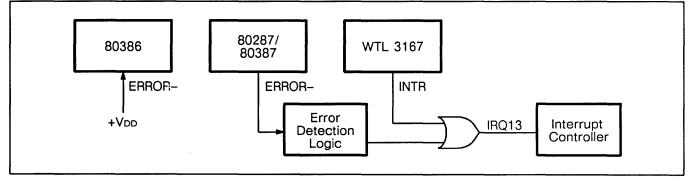

The INTR output of the WTL 3167 must be connected to the system interrupt controller. In the world of ATcompatible systems, for example, the WTL 3167 INTR should be "ORed" to the 80287/80387 interrupt logic and the output should be connected to IRQ13 as shown in figure 7.

#### WTL 3167 PRESENT (PRES-)

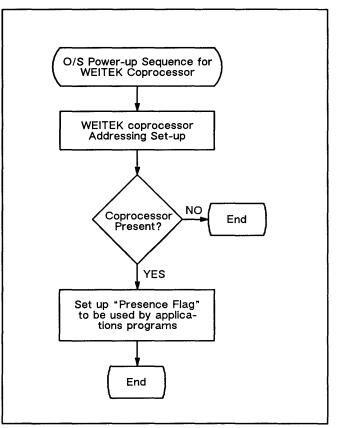

PRES- signals the presence of a WTL 3167 coprocessor. This signal should be connected to VCC through a resistor of at least 10KOhm to insure a high level when the WEITEK coprocessor is not present.

The basic software method of detecting the presence of a WTL 3167 in an 80386 system is to perform a functional test of the device by attempting to load data into the coprocessor register file and read it back (a coded example is provided in figure 56 on page 51. The hardware designer can use the PRES- output to make sure that the system generates a READY- signal when the WTL 3167 is addressed but is absent, (as determined by PRES- being high), in order to avoid system hangs.

#### NO CONNECTION

NC pins on the outer rows and columns are reserved for future expansion and should be left unconnected.

#### OTHER PINS

CKM, PEREQ, BUSY-, 387 CLK2, ERROR-, READYO-, STEN, CMDO, and pins L4 and M10 are only used by the 80387 coprocessor. Refer to the 80387 data sheet for details. Such signals can be left unconnected if the WTL 3167 is the only coprocessor that will ever be used.

#### DECOUPLING CAPACITORS

Decoupling capacitors should be placed on each side of the EMC socket, as shown in figure 3.

#### SYSTEM-LEVEL CONSIDERATIONS

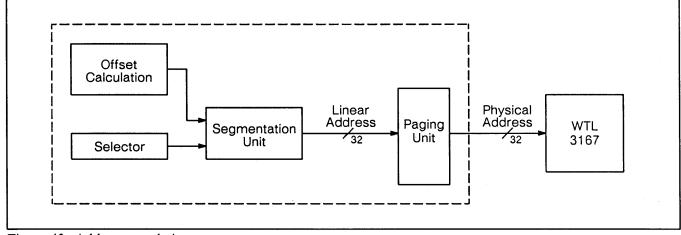

The WTL 3167 coprocessor is a memory-mapped peripheral that communicates with the 80386 over the same address bus that connects the main memory to the CPU. Instructions are defined by the 14 least-significant address bits (A15..2) as well as three of the four byte enables (BE2..0-).

The seven most-significant bits of the 80386 address bus (A31..25), together with the Memory I/O control Signal (M/IO-), select the WTL 3167 coprocessor. Only the upper seven address bits are decoded to determine when a coprocessor operation is being requested.

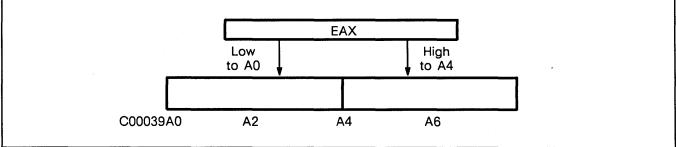

The coprocessor will respond to memory addresses C0000000 through C1FFFFF hex. Although by convention only addresses C0000000 to C000FFFF hex are used, it is important to be sure that other components in the system do not conflict with the address space decoded by the coprocessor. Writing to this address space will cause the WTL 3167 to execute instructions and reading will cause the coprocessor to drive the data bus.

#### TESTING THE DESIGN

A set of diagnostic routines that test the coprocessor design for both UNIX and DOS, real and protected mode environments, is available from WEITEK. No WTL 3167 programming knowledge is required to run the diagnostics software. Contact your WEITEK sales engineer for a copy of the diagnostics. (Refer to figure 21 on page 20 for the product's part number.)

Figure 7. Interrupt output connection in an AT-compatible system

#### PRELIMINARY DATA September 1988

## Hardware Designer's Section, continued

#### SPECIFICATIONS

#### ABSOLUTE MAXIMUM RATINGS

| Supply voltage | –0.5 to 7.0 V   |

|----------------|-----------------|

| Input voltage  | 0.5 to VDD      |

| Output voltage | . $-0.5$ to VDD |

Storage Temperature Range ...... -65°C to 150°C Operating Temperature Range ...... 0°C to 85°C

#### RECOMMENDED OPERATING CONDITIONS

| P                              |                 | Comn |      |      |

|--------------------------------|-----------------|------|------|------|

| Parameter                      | Test Conditions | Min  | Max  | Unit |

| V <sub>DD</sub> Supply Voltage |                 | 4.75 | 5.25 | v    |

| Tcase Operating Temperature    |                 | 0    | 85   | °C   |

Figure 8.

#### DC ELECTRICAL CHARACTERISTICS

| Develope         |                                  | <b>T</b>                                 | Comn              |                     |      |

|------------------|----------------------------------|------------------------------------------|-------------------|---------------------|------|

|                  | Parameter                        | Test Conditions                          | Min               | Max                 | Unit |

| VIH              | High-level input voltage         | V <sub>DD</sub> = MAX                    | 2.0               |                     | V    |

| V <sub>IL</sub>  | Low-level input voltage          | V <sub>DD</sub> = MIN                    |                   | 0.8                 | ٧    |

| VIHC             | CLK2 Input high voltage          | V <sub>DD</sub> = MIN/MAX                | V <sub>DD</sub> 8 | V <sub>DD</sub> +.3 | ۷    |

| V <sub>ILC</sub> | CLK2 Input low voltage           | V <sub>DD</sub> = MIN                    |                   | 0.8                 | V    |

| V <sub>OH</sub>  | High-level output voltage        | $V_{DD} = MIN, I_{OH} = -1.0 \text{ mA}$ | 2.4               |                     | V    |

| V <sub>OL</sub>  | Low-level output voltage         | $V_{DD}$ = MIN, $I_{OL}$ = 4.0 mA        |                   | 0.4                 | ۷    |

| I <sub>IHc</sub> | CLK2<br>High-level input current | $V_{DD} = MAX, V_{IN} = V_{DD}$          |                   | ±10                 | μA   |

| I <sub>ILC</sub> | CLK2<br>Low-level input current  | $V_{DD} = MAX, V_{IN} = 0V$              |                   | ±10                 | μA   |

| I <sub>IH</sub>  | High-level input current         | $V_{DD} = MAX, V_{IN} = V_{DD}$          |                   | ±10                 | μA   |

| ۱,_              | Low-level input current          | $V_{DD} = MAX, V_{IN} = 0V$              |                   | ±10                 | μA   |

| I <sub>cc</sub>  | Supply current                   | $CLK2 = MIN, V_{DD} = MAX$               |                   | 350                 | mA   |

|                  | WARNING! R                       | emove power before insertion or remov    | val.              |                     |      |

Figure 9. DC electrical characteristics over recommended temperature range

## Hardware Designer's Section, continued

### AC SWITCHING CHARACTERISTICS

|                                                           | pol Parameter                                                                                                                                                                                                                                                                                                                                                                 |                                                            | -016                                                 | 3167                                      | 020               | 3167 | -025     |      | Ref                       |                  |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------|-------------------------------------------|-------------------|------|----------|------|---------------------------|------------------|

| Symbol                                                    | Parameter                                                                                                                                                                                                                                                                                                                                                                     | Min                                                        | Max                                                  | Min                                       | Max               | Min  | Max      | Unit | Figure                    | Notes            |

| 2T <sub>CY</sub>                                          | Clock Cycle Time                                                                                                                                                                                                                                                                                                                                                              | 62                                                         |                                                      | 50                                        |                   | 40   |          | ns   | 12                        |                  |

| Tcy                                                       | CLK2 Period                                                                                                                                                                                                                                                                                                                                                                   | 31                                                         |                                                      | 25                                        |                   | 20   |          | ns   | 12                        |                  |

| T <sub>CHa</sub>                                          | CLK2 High Time                                                                                                                                                                                                                                                                                                                                                                | 9                                                          |                                                      | 8                                         |                   | 7.5  |          | ns   | 12                        | At 2V            |

| Тснь                                                      | CLK2 High Time                                                                                                                                                                                                                                                                                                                                                                | 8                                                          |                                                      | 7                                         |                   | 6.5  |          | ns   | 12                        | At 2.5V          |

| T <sub>CLa</sub>                                          | CLK2 Low Time                                                                                                                                                                                                                                                                                                                                                                 | 9                                                          |                                                      | 8                                         |                   | 7.5  |          | ns   | 12                        | At 2V            |

| TCLb                                                      | CLK2 Low Time                                                                                                                                                                                                                                                                                                                                                                 | 7                                                          |                                                      | 7                                         |                   | 6.5  |          | ns   | 12                        | At 0.8V          |

| TR                                                        | Clock Rise Time                                                                                                                                                                                                                                                                                                                                                               |                                                            | 8                                                    |                                           | 8                 |      | 7        | ns   | 12                        |                  |

| TF                                                        | Clock Fall Time                                                                                                                                                                                                                                                                                                                                                               |                                                            | 8                                                    |                                           | 8                 |      | 7        | ns   | 12                        |                  |

| T <sub>1</sub>                                            | ADS-, W/R- Setup Time                                                                                                                                                                                                                                                                                                                                                         | 27                                                         |                                                      | 17                                        |                   | 15   |          | ns   | 13,14,15,<br><u>16,17</u> | Notes 1, 3, 5    |

| T <sub>2</sub>                                            | ADS- Hold Time                                                                                                                                                                                                                                                                                                                                                                | 4                                                          |                                                      | 4                                         |                   | 4    |          | ns   | 13,14,15,<br>16,17        | Notes 1, 3       |

| T <sub>3</sub>                                            | A <sub>152</sub> , BE <sub>20</sub> - Setup Time                                                                                                                                                                                                                                                                                                                              | 22                                                         |                                                      | 18                                        |                   | 15   |          | ns   | 13,14,15,<br>16,17        | Notes 1, 3, 5    |

| T4                                                        | A <sub>152</sub> , BE <sub>20</sub> - W/R- Hold Time                                                                                                                                                                                                                                                                                                                          | 4                                                          |                                                      | 4                                         |                   | 4    |          | ns   | 13,14,15,<br>16,17        | Notes 1, 3, 6    |

| T <sub>5</sub>                                            | M/IO-, A <sub>3125</sub> Setup Time                                                                                                                                                                                                                                                                                                                                           | 11                                                         |                                                      | 8                                         |                   | 7    |          | ns   | 13,14,15,<br>16,17        | Notes 1, 3, 5    |

| T <sub>6</sub>                                            | M/IO-, A3125 Hold Time                                                                                                                                                                                                                                                                                                                                                        | 4                                                          |                                                      | 4                                         |                   | 4    |          | ns   | 13,14,15,<br>16,17        | Notes 1, 3, 6    |

| T <sub>7</sub>                                            | D <sub>310</sub> Setup Time                                                                                                                                                                                                                                                                                                                                                   | 20                                                         |                                                      | 20                                        |                   | 20   |          | ns   | 13,14,16                  | Notes 1, 3, 4, 5 |

| T <sub>8</sub>                                            | D <sub>310</sub> Hold Time                                                                                                                                                                                                                                                                                                                                                    | 2                                                          |                                                      | 2                                         |                   | 2    |          | ns   | 13,14,16                  | Notes 1, 3, 4, 6 |

| T9                                                        | READY- Setup Time                                                                                                                                                                                                                                                                                                                                                             | 20                                                         |                                                      | 12                                        |                   | 9    |          | ns   | 13,14,15,<br>16,17        | Notes 1, 3       |

| T <sub>10</sub>                                           | READY- Hold Time                                                                                                                                                                                                                                                                                                                                                              | 4                                                          |                                                      | 4                                         |                   | 4    |          | ns   | 13,14,15,<br>16,17        | Notes 1, 3       |

| T11                                                       | D <sub>310</sub> Output Delay                                                                                                                                                                                                                                                                                                                                                 |                                                            | 48                                                   |                                           | 38                |      | 30       | ns   | 15,17                     | Notes 1, 3, 12   |

| T <sub>12</sub>                                           | D <sub>310</sub> Valid Output                                                                                                                                                                                                                                                                                                                                                 | 6                                                          |                                                      | 6                                         |                   | 5    |          | ns   | 15,17                     | Notes 1, 3       |

| T <sub>13</sub>                                           | D <sub>310</sub> Float Delay                                                                                                                                                                                                                                                                                                                                                  |                                                            | 35                                                   |                                           | 27                |      | 22       | ns   | 15,17                     | Notes 3, 8, 13   |

| T <sub>14</sub>                                           | RESET Setup Time                                                                                                                                                                                                                                                                                                                                                              | 12                                                         |                                                      | 12                                        |                   | 10   |          | ns   | 18                        | Notes 1, 3       |

| T <sub>15</sub>                                           | RESET Hold Time                                                                                                                                                                                                                                                                                                                                                               | 4                                                          |                                                      | 4                                         |                   | 3    |          | ns   | 18                        | Notes 1, 3       |

|                                                           |                                                                                                                                                                                                                                                                                                                                                                               |                                                            | Contin                                               | ued ne                                    | kt page           |      |          |      |                           |                  |

| 1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9.<br>10. | All parameters are specified at 1<br>All output delays are specified at 1<br>Relative to CLK2 rising edge<br>Write bus cycle only<br>Referenced to end of cycle when<br>Hold time reference to end of cycl<br>Delay is measured with respect to<br>One CLK2 period<br>Spec only applies when TCB- is h<br>Spec only applies when TCB- is s<br>85 pf loading<br>120 pf loading | .5V unle<br>1.5V w<br>ADS- i<br>cle whei<br>o M/IO-<br>igh | ess othe<br>ith 50 p<br>s de-as<br>n ADS i<br>-, A31 | erwise r<br>f loadin<br>serted<br>s asser | noted<br>g unles: |      | wise not | ed   |                           |                  |

12. 120 pf loading

13. Tri-State timing is guaranteed, but not tested

Figure 10. AC characteristics

1

#### PRELIMINARY DATA September 1988

## Hardware Designer's Section, continued

| Symbol                           | Deverseter                                                                                                                                                                                                                                                                             | 3167                                   | -016                                        | 3167–020                                  |                    | 3167-025  |           |           | Ref                |                    |     |     |     |     |     |      |        |       |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------|-------------------------------------------|--------------------|-----------|-----------|-----------|--------------------|--------------------|-----|-----|-----|-----|-----|------|--------|-------|--|

| Symbol                           |                                                                                                                                                                                                                                                                                        |                                        | Parameter                                   | Parameter                                 | Parameter          | Parameter | Parameter | Parameter | Parameter          | Min                | Мах | Min | Мах | Min | Мах | Unit | Figure | Notes |  |

| T <sub>16</sub>                  | INTR Output Delay                                                                                                                                                                                                                                                                      |                                        | 72                                          |                                           | 62                 |           | 50        | ns        | 19                 | Notes 1, 3         |     |     |     |     |     |      |        |       |  |

| T <sub>17</sub>                  | INTR Valid Output                                                                                                                                                                                                                                                                      | 6                                      |                                             | 6                                         |                    | 5         |           | ns        | 19                 | Notes 1, 3         |     |     |     |     |     |      |        |       |  |

| T <sub>18</sub>                  | MCS- Output Delay                                                                                                                                                                                                                                                                      |                                        | 25                                          |                                           | 20                 |           | 17        | ns        | 13,17              | Notes 1, 7         |     |     |     |     |     |      |        |       |  |

| T <sub>19A</sub>                 | RDY- Output Delay (high to low)                                                                                                                                                                                                                                                        |                                        | 26                                          |                                           | 24                 |           | 22        | ns        | 13,14,15,<br>16,17 | Notes 1, 3, 9, 11  |     |     |     |     |     |      |        |       |  |

| T <sub>19B</sub>                 | RDY- Output Delay (low to high)                                                                                                                                                                                                                                                        |                                        | 26                                          |                                           | 24                 |           | 22        | ns        | 14,16,15           | Notes 1, 3, 9, 11  |     |     |     |     |     |      |        |       |  |

| T <sub>20</sub>                  | RDY- Valid Output                                                                                                                                                                                                                                                                      | 4                                      |                                             | 4                                         |                    | 4         |           | ns        | 13,15,<br>16,17    | Notes 1, 3, 9, 11  |     |     |     |     |     |      |        |       |  |

| T <sub>21</sub>                  | RDY- Tri-State Enable                                                                                                                                                                                                                                                                  |                                        | 25                                          |                                           | 25                 |           | 20        | ns        | 14,15,<br>16,17    | Notes 3, 10, 11, 1 |     |     |     |     |     |      |        |       |  |

| T <sub>22</sub>                  | RDY- Tri-State Disable                                                                                                                                                                                                                                                                 | 5                                      | 25                                          | 5                                         | 25                 |           | 20        | ns        | 14,15,<br>16,17    | Notes 3, 10, 11, 1 |     |     |     |     |     |      |        |       |  |

| T <sub>23</sub>                  | AF32- Tri-State Enable                                                                                                                                                                                                                                                                 |                                        | 31                                          |                                           | 25                 |           | 20        | ns        | 14,15,<br>16,17    | Notes 3, 10, 13    |     |     |     |     |     |      |        |       |  |

| T <sub>24</sub>                  | AF32- Tri-State Disable                                                                                                                                                                                                                                                                |                                        | 31                                          |                                           | 25                 |           | 20        | ns        | 14,15,<br>16,17    | Notes 3, 10, 13    |     |     |     |     |     |      |        |       |  |

| T <sub>25</sub>                  | AF32- Output Delay                                                                                                                                                                                                                                                                     |                                        | 31                                          |                                           | 25                 |           | 20        | ns        | 14,15,<br>16,17    | Notes 3, 10        |     |     |     |     |     |      |        |       |  |

| T <sub>26</sub>                  | AF32- Valid Output                                                                                                                                                                                                                                                                     | 3                                      |                                             | 3                                         |                    | 2         |           | ns        | 15                 | Notes 3, 10        |     |     |     |     |     |      |        |       |  |

| 1.<br>2.<br>3.<br>4.<br>5.<br>6. | All parameters are specified at 1.<br>All output delays are specified at 1.<br>All output delays are specified at<br>Relative to CLK2 rising edge<br>Write bus cycle only<br>Referenced to end of cycle when<br>Hold time reference to end of cyc<br>Delay is measured with respect to | 5V unle<br>1.5V w<br>ADS- i<br>cle whe | ess othe<br>ith 50 p<br>is de-as<br>n ADS i | erwise r<br>f loadin<br>serted<br>s asser | noted<br>Ig unles: |           | wise no   | ted       |                    |                    |     |     |     |     |     |      |        |       |  |

- 7. Delay is measured with respect to W/IO-, A3

8. One CLK2 period

9. Spec only applies when TCB- is high

10. Spec only applies when TCB- is strapped low

11. 85 pf loading

- 12. 120 pf loading

- 13. Tri-State timing is guaranteed, but not tested

Figure 10. AC characteristics, continued

## Hardware Designer's Section, continued

TIMING

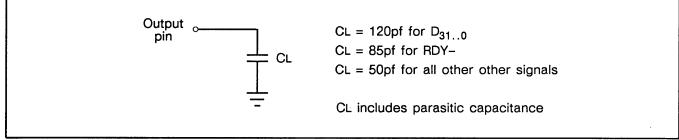

## Figure 11. Test load for delay measurement

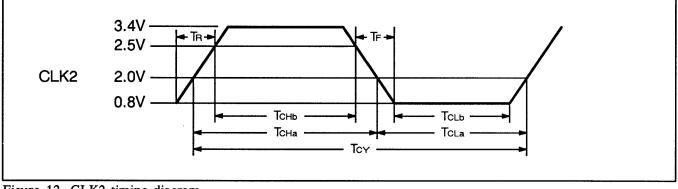

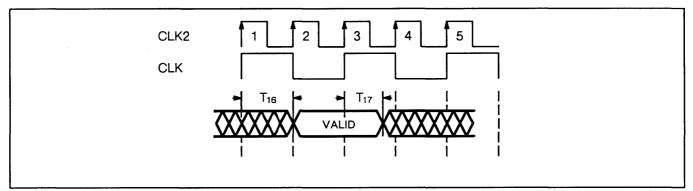

Figure 12. CLK2 timing diagram

#### PRELIMINARY DATA September 1988

### Hardware Designer's Section, continued

#### NON-PIPELINED BUS CYCLES

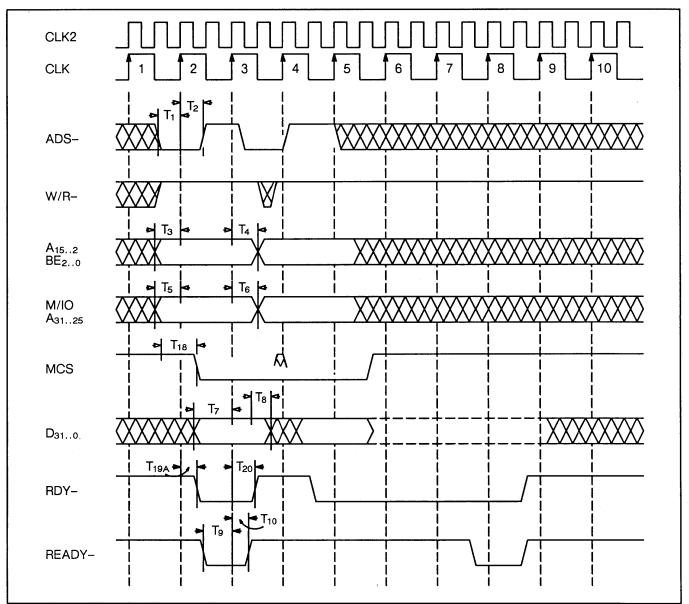

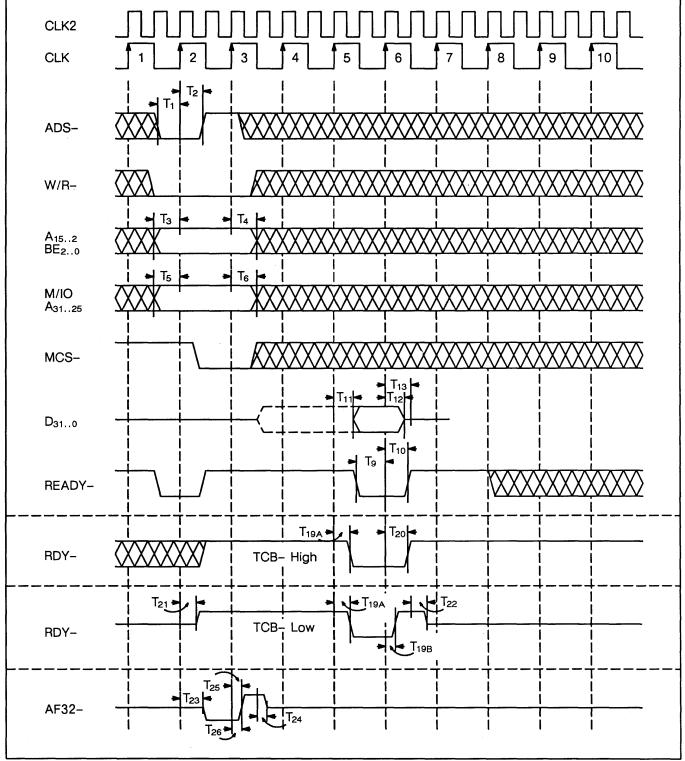

Figure 13 shows two WTL 3167 write cycles with TCBhigh, or NC. Write cycles are performed every time the 80386 broadcasts instructions to the coprocessor. The RDY- output of the WTL 3167 handles the handshaking between the WTL 3167 and the 80386. To acknowledge the current bus cycle, the WTL 3167 asserts RDY- and the 80386 terminates the bus cycle. The first bus write operation does not have the READY- input delayed while the second does. In the delayed READY- write operation, even though the bus does not advance and  $D_{31..0}$  is held constant, it is latched in the same cycle it would be if READY- were not delayed. Thus, if the data changes in the time slots indicated in figure 13 with crosshatching, the new data is not used by the WTL 3167.

Figure 13. Non-pipelined bus write cycle with and without delayed ready, TCB- high, or NC

## Hardware Designer's Section, continued

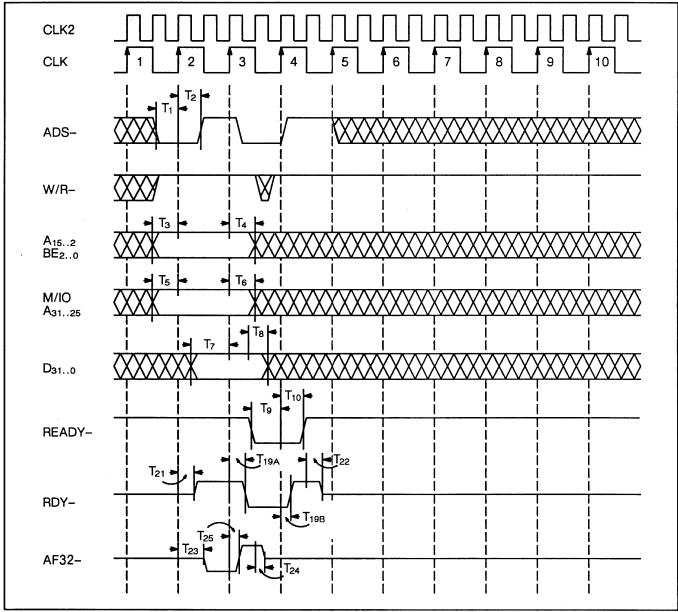

Figure 14 shows a new pipelined bus write cycle with TCB- low. The bus cycle now takes a minimum of three clock cycles.

Figure 14. Non-pipelined bus write cycle without delayed ready, TCB- low

#### PRELIMINARY DATA September 1988

### Hardware Designer's Section, continued

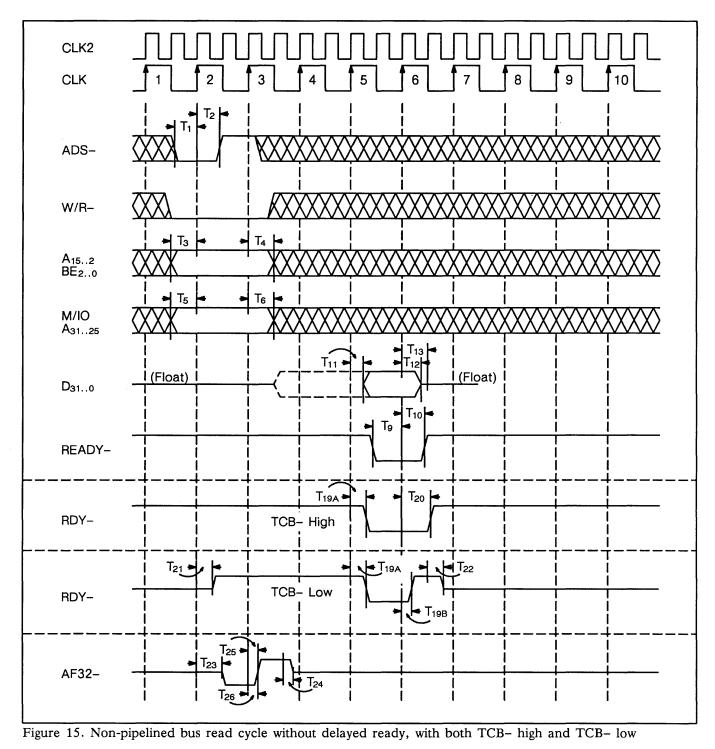

Read cycles are performed every time data must be read from the WTL 3167 into the 80386. Figure 15 shows a typical WTL 3167 read cycle. At least one wait state is always inserted during a read cycle to allow the WTL 3167 time to respond. As shown in figure 15, the minimum read cycle takes the same number of clock cycles, independent of the value of TCB-. Wait states are fully transparent to the programmer. If READY- is delayed, the data will continue to be driven until READY- is asserted. When the WTL 3167 receives a bus read operation, it turns on its bus drivers even before the data is ready. The dotted lines in figure 15 shows the time slots during which the WTL 3167 is driving the bus with invalid data. Valid data is only present when RDY- is asserted.

## Hardware Designer's Section, continued

#### PRELIMINARY DATA September 1988

### Hardware Designer's Section, continued

### PIPELINED BUS CYCLES

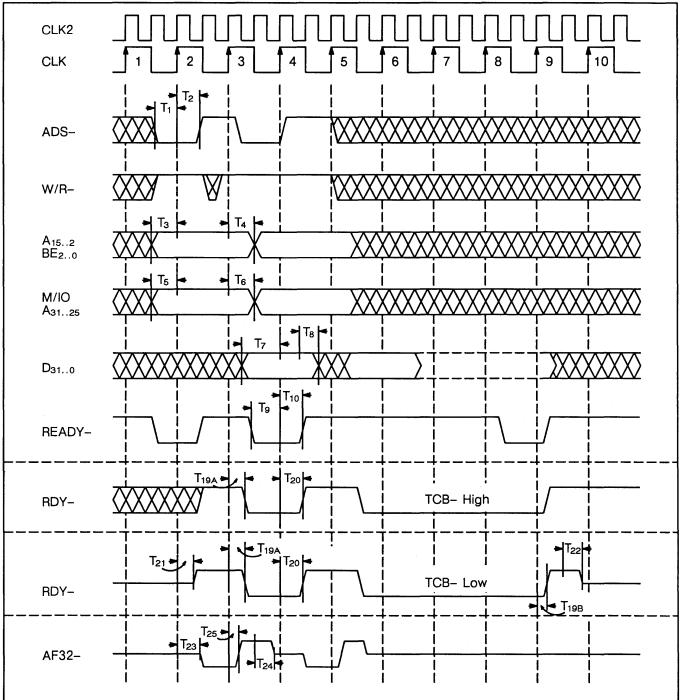

The WTL 3167 is capable of operating with or without address pipelining on a cycle-by-cycle basis. It uses ADS- and READY- from the 80386 to determine when a bus cycle begins. Figure 16 shows a typical pipelined

write cycle. The minimum write bus cycle takes the same number of clock cycles, independent of the value of TCB-.

Figure 16. Pipelined bus write cycle without and with delayed ready, and with both TCB- high and TCB- low

## Hardware Designer's Section, continued

Figure 17 shows a typical pipelined read cycle.

#### PRELIMINARY DATA September 1988

## Hardware Designer's Section, continued

### RESET AND INTERRUPT TIMING

RESET set-up and hold time and interrupt valid delays are shown in figures 18 and 19. RESET must be synchronous with the 80386's clock to guarantee proper operation.

Figure 18. RESET timing

Figure 19. Interrupt timing

### Software Tools Overview

The WTL 3167 coprocessor is supported by the UNIX operating system (System V release 3.0). Operating system support includes coprocessor addressing, presence detection at power-up, context-switch handling and emulation. For UNIX operating systems information contact your UNIX supplier. XENIX 386 support is forthcoming.

The WTL 3167 is also supported by Phar Lap, IGC, and AI architects MS-DOS protected mode environments. MS-DOS protected mode environment support for the WTL 3167 includes coprocessor addressing and presence detection.

The WEITEK coprocessor can be supported under real mode MS-DOS as well. OEMs that intend to provide MS-DOS real mode support for the WEITEK coprocessor must refer to the Systems Programmer's section.

C, FORTRAN and Pascal Compilers for the 80386 and WTL 3167 under UNIX V.3 and MS-DOS protected mode are provided by Green Hills, Metaware, Microway, and Silicon Valley Software. Lahey Computer Systems offers an MS-DOS real mode FORTRAN compiler. Metaware also provides MS-DOS real mode C and Pascal compilers. Contact vendors for details.

The WEITEK Coprocessor is fully transparent to the programmer using these compilers, as the floating-point operations are specified with familiar high-level language commands. The compilers include a run-time library for transcendental operations.

Compiler designers and programmers who intend to write WTL 3167 assembly code should refer to the Applications Programmer's section. Systems programmers who need to modify existing operating systems to support the WTL 3167 should refer to the Systems Programmer's section.

#### TRANSCENDENTAL ROUTINES LIBRARY

WEITEK provides a library of transcendental routines to compiler developers. Routines are available through a simple license agreement.

| Vendor                     | Product                                               | Phone          |

|----------------------------|-------------------------------------------------------|----------------|

| AI Architects              | OS 386 (MS-DOS protected mode environment)            | (617) 577-8052 |

| Green Hills Software       | C, F, P Compilers (UNIX and MS-DOS protected mode)    | (818) 246-5555 |

| IGC                        | X-AM (MS-DOS protected mode environment)              | (408) 986–8373 |

| Lahey Computer Systems     | F Compiler (MS-DOS real mode)                         | (702) 831–2500 |

| Metaware                   | C, P Compilers (UNIX, MS-DOS real and protected mode) | (408) 429–6382 |

| Microway                   | C, F, P Compilers (UNIX and MS-DOS protected mode)    | (617) 746–7341 |

| Phar-Lap Software          | RUN386 (MS-DOS protected mode environment)            | (617) 661–1510 |

| Silicon Valley Software    | C, F, P Compilers (UNIX and MS-DOS protected mode)    | (408) 725-8890 |

| Note: F = Fortran, P = Pas | scal                                                  |                |

Figure 20. Software tools information

| Product                    | Part Number  |

|----------------------------|--------------|

| UNIX Diagnostics           | 4800–1167–02 |

| DOS Diagnostics and Macros | 4800-1167-03 |

| DOS Demos                  | 4800–1167–04 |

Figure 21. WEITEK-supplied support software

#### PRELIMINARY DATA September 1988

#### **Applications Programmer's Section**

This section provides the information necessary to program the WTL 3167 coprocessor in 80386 assembly language. It is complemented by the WTL 1167 Software Designer's Guide. The WTL 3167 is a code-compatible upgrade of the WTL 1167 coprocessor daughter board.

The WTL 3167 internal registers and instruction set are first described in detail. Programming the WEITEK coprocessor can be greatly simplified by defining a set of macro instructions. Macro examples and a simple programming example are part of this section.

#### REGISTERS

The WTL 3167 provides a register set of 32 single-precision registers, named ws0 through ws31. Pairs of WTL 3167 registers can be used for double-precision operations, allowing up to 16 double-precision registers, numbered wd0, wd2, wd4, ..., wd30. The MSW is stored in the even register and the LSW is stored in the next contiguous odd register (that is, MSW in wsN, LSW in wsN+1). In addition, any 80386 doubleword register can be used to move data, or as the source operand to an arithmetic instruction. The use of register ws0 is restricted. (Refer to page 34 for more details on register ws0.)

#### PROCESS CONTEXT REGISTER

The WTL 3167 also provides a 32-bit process context register (PCR), which can be written to control

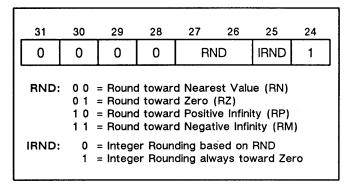

rounding modes and exception handling. The context register can also be read to save control settings and read various status flags. The format of this register is defined in figure 23.

#### MODE SELECTION FIELD

The uppermost byte of the process context register includes the mode selection field and the mode field.

The mode selection field (MDSEL) is used during system initialization to set the mode register in the floating-point chips. If MDSEL is set to 1100 when loading the Context Register, only the EM, CC, and AE fields are updated. If MDSEL is set to 0000 the EM, CC, AE fields, and the rounding mode field (MD) are updated. (See figure 24.)

|      | 1        |                  |      |

|------|----------|------------------|------|

| wd0  | <b>→</b> | ws0 (Restricted) | ws1  |

| wd2  | <b>→</b> | ws2              | ws3  |

| wd4  | <b>→</b> | ws4              | ws5  |

| :    |          |                  | :    |

| wd30 | <b>→</b> | ws30             | ws31 |

Figure 22. WTL 3167 register file

| <u>31 28 27 24 23 16 15 8 7</u> |  |

|---------------------------------|--|

| MDSEL MD EM CC AE               |  |

Figure 23. Process context register

#### MODE FIELD

The mode field (MD) is used to specify rounding options. Two bits specify one of four rounding modes as defined by the IEEE standard (RN, RZ, RP, RM). A third bit determines the rounding mode used in floating-point-to-integer conversion instructions. It selects either the current rounding mode or the round-to-zero mode. The least-significant bit of the mode field specifies fast mode, (see *IEEE Considerations*, page 42) and must always be set to 1.

#### ACCUMULATED EXCEPTION FIELD

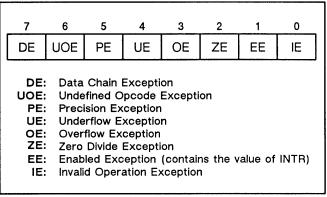

The accumulated exception field (AE) contains the five exception flags required by the IEEE standard and other WTL 3167-specific exceptions. The AE field is cleared by writing zeros into the corresponding bits of byte zero of the PCR. The accumulated exception flags are formed by the logic "OR" of the AE field and the current instruction's exception status. The flags accumulate all exceptions which have occurred since the user last cleared the AE field. Exceptions are accumulated regardless of the value of the corresponding exception mask field.

The AE field is shown in figure 25.

#### EXCEPTION MASK FIELD

The next lower PCR byte is the exception mask field (EM). Seven bits are used to enable exception traps. At the conclusion of an instruction, the accumulated exception field is updated and, if an exception occurred and the corresponding bit in the EM field is set low, the WTL 3167 generates an 80386 interrupt by driving the interrupt request output high. The exception mask byte is shown in figure 26.

Most of the exceptions have the same name as a corresponding 80387 exception and work the same way. The WTL 3167 has an undefined opcode exception, flagged whenever the instruction broadcast by the 80386 is not recognized as a WEITEK instruction. The invalid operation exception is flagged when an invalid operation occurs. The data chain exception is never flagged by the WTL 3167. It has been documented for consistency with the WTL 1167 product. (For a detailed description of the WTL 3167 exception handling refer to *IEEE Considerations*, page 42.)

Figure 24. Mode field

Figure 25. Accumulated exception field

| 23                                                                                                                                                                                                                                             | 22  | 21 | 20 | 19 | 18 | 17 | 16 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|----|----|----|----|----|--|

| DM                                                                                                                                                                                                                                             | UOM | PM | UM | ОМ | ZM | 1  | IM |  |

| DM: Data Chain exception Mask<br>UOM: Undefined Opcode exception Mask<br>PM: Precision exception Mask<br>UM: Underflow exception Mask<br>OM: Overflow exception Mask<br>ZM: Zero Divide exception Mask<br>IM: Invalid Operation exception Mask |     |    |    |    |    |    |    |  |

Figure 26. Exception mask field

## PRELIMINARY DATA

September 1988

### Applications Programmer's Section, continued

#### CONDITION CODE FIELD

The Condition Code Field (CC) is updated only when test or compare instructions are executed. The CC field is updated to reflect the status of the compare operation. At the end of the compare operation the coprocessor status output is encoded and stored in PCR<sub>15..8</sub>. The encoding is shown in figure 27.

#### INSTRUCTION SET

WTL 3167 instructions can be divided into:

- 1. Data movement instructions

- 2. Format conversion instructions

- 3. Arithmetic instructions

- 4. Compare and test instructions

- 5. Sign manipulation instructions

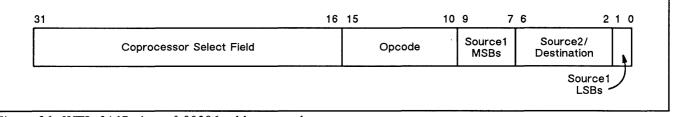

Most WTL 3167 instructions operate on either two WTL 3167 registers or on one WTL 3167 register and the contents of the 80386 data bus. WEITEK coprocessor macro instructions have the format:

OPCODE Source2/Destination, Source1

Source1 and Source2/Destination specify the operand addresses. The operation result is always stored in the same location as Source2. While Source2/Destination always specifies one of the thirty-two WTL 3167 internal registers, Source1 can either specify an internal

register (for register-to-register operations), an immediate constant or the content of a 80386 register (for memory-to-register operations).

#### DATA MOVEMENT INSTRUCTIONS

Data movement instructions move data between the 80386 and a WTL 3167 register, or between two WTL 3167 registers.

| I                                               | z  | C2 | C0 | N         | leanin    | g         |    |

|-------------------------------------------------|----|----|----|-----------|-----------|-----------|----|

|                                                 | 1  | 0  | 0  | Equal     |           | Equal     |    |

|                                                 | 0  | 0  | 1  | Less than |           | Less than |    |

|                                                 | 0  | 0  | 0  | Gre       | ater th   | nan       |    |

|                                                 | 1  | 1  | 1  | Unc       | Unordered |           |    |

| 15                                              | 14 | 13 | 12 | 11        | 10        | 9         | 8  |

| X                                               | Z  | 0  | x  | х         | C2        | Х         | C0 |

| X: not defined<br>0: bit 13 must be set to zero |    |    |    |           |           |           |    |

Figure 27. Condition code field

| 1 |         |                |                                                             |

|---|---------|----------------|-------------------------------------------------------------|

|   | WFLD    | ws1, ws2       | ; load ws1 from ws2                                         |

|   | WFLD    | ws21, EAX      | ; load ws21 from EAX                                        |

|   | WFLD    | ws4, Pl        | ; load ws4 with constant PI (declared elsewhere)            |

|   | WFLD    | wd4, wd12      | ; load ws4 from ws12, then load ws5 from ws13               |

|   | WFLDCTX | EAX            | ; load Context Register from EAX                            |

|   | WFPOP   | ws1            | ; pop a number from 386 stack to ws1                        |

|   | WFLDSD  | ws1, ARRAY, 31 | ; load 31 numbers from ARRAY to registers ws1 through ws31  |

|   | WFLDSD  | ws10, ESI, ECX | ; load ECX numbers from ESI to registers starting with ws10 |

|   | WFST    | EDX, ws21      | ; store ws21 to EDX                                         |

|   | WFSTCTX | EAX            | ; store Context register to EAX                             |

|   | WFPUSH  | ws1            | ; push ws1 onto the 386 stack                               |

|   | WFSTSD  | ws0, ARRAY, 32 | ; store all 32 registers to ARRAY                           |

|   | WFSTSD  | ws10, EDI, ECX | ; store ECX registers from ws10 to EDI                      |

|   | WFSTRL  | EAX            | ; store revision level to EAX                               |

|   |         |                |                                                             |

Figure 28. Examples of data movement instructions

#### FORMAT CONVERSION INSTRUCTIONS

The WTL 3167 provides instructions for converting from any data type supported (single-precision, double-precision, 32-bit integer) to any other type. See figure 29.

| WFLOAT<br>WFLOAT<br>WFLOAT<br>WFLOAT<br>WFLOAT<br>WFIX<br>WFIX<br>WFIX<br>WFIX<br>WFIX<br>WFCVT<br>WFCVT | ws1, ws10<br>wd4, ws13<br>ws3, EAX<br>wd6, EBX<br>wd10, 123456<br>ws1, ws4<br>ws3, wd10<br>ws5, EBX<br>ws1, wd14<br>ws8, EBX | <ul> <li>; convert integer ws10 to single-precision ws1</li> <li>; convert integer ws13 to double-precision wd4</li> <li>; convert integer EAX to single-precision ws3</li> <li>; convert integer EBX to double-precision wd6</li> <li>; load wd10 with the constant 123456.0</li> <li>; convert single-precision ws4 to integer ws1</li> <li>; convert double-precision wd10 to integer ws3</li> <li>; convert single-precision EBX to integer ws5</li> <li>; convert double-precision wd14 to single-precision ws1</li> <li>; convert double-precision (EBX, ws1) to single-precision ws8</li> </ul> |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                          |                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WFCVT<br>WFCVT                                                                                           | wd10, ws9<br>wd26, EAX                                                                                                       | ; convert single-precision ws9 to double-precision wd10<br>; convert single-precision EAX to double-precision wd26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Figure 29. Examples of format conversion instructions

#### PRELIMINARY DATA September 1988

#### Applications Programmer's Section, continued

#### ARITHMETIC INSTRUCTIONS

The WTL 3167 provides the four basic arithmetic functions as well as square root. In the subtraction instruction, the Source2/Destination operand is subtracted from the Source1 operand. The reverse subtraction reverses the operands from the standard subtract instruction. The division instruction divides the Source1 operand by the Source2/Destination. The single-precision multiply/accumulate operation multiplies the operands specified by Source1 and Source2 and adds the result to the contents of register ws2. The double-precision multiply/accumulate operation with single-precision inputs multiplies the single-precision operands specified by Source1 and Source2 and adds the result to the contents of register wd2. The doubleprecision multiply/accumulate operation with doubleprecision inputs multiplies the double-precision operands specified by Source1 and Source2 and adds the result to the contents of register wd2.

| WFADD  | ws6, ws13  | ; add ws13 into ws6                                |

|--------|------------|----------------------------------------------------|

| WFADD  | wd14, wd20 | ; add wd20 into wd14                               |

| WFADD  | ws3, EAX   | ; add EAX into ws3                                 |

| WFADD  | wd2, EBX   | ; add (EBX, ws1) into wd2                          |

| WFADD  | ws1, 9.0   | ; add the constant 9.0 into ws1                    |

| WFSUBR | ws5, ws30  | ; set ws5 to ws30 – ws5                            |

| WFSUBR | wd12, wd14 | ; set wd12 to wd14 - wd12                          |

| WFSUBR | ws3, EDX   | ; set ws3 to EDX – ws3                             |

| WFSUB  | ws5, ws30; | ; set ws5 to ws5 – ws30                            |

| WFSUB  | ws8, EDX   | ; set ws8 to ws8 – EDX                             |

| WFMUL  | ws1, ws2   | ; multiply ws2 into ws1                            |

| WFMULN | wd4, wd6   | ; set wd4 to (– wd4 $	imes$ wd6)                   |

| WFAMUL | ws5, EAX   | ; set ws5 to the absolute value of ws5 $	imes$ EAX |

| WFMUL  | ws23, 2.0  | ; multiply the constant 2.0 into ws23              |

| WFMAC  | ws10, ws11 | ; add ws10 $	imes$ ws11 into ws2                   |

| WFMAC  | ws9, EAX   | ; add ws9 $	imes$ EAX into ws2                     |

| WFMACD | ws13, ws29 | ; add ws13 $\times$ ws29 into wd2                  |

| WFMACD | ws1, EBP   | ; add ws1 $\times$ EBP into wd2                    |

| WFMACD | wd12, wd28 | ; add wd12 $\times$ wd28 into wd2                  |

| WFDIVR | ws3, ws5   | ; set ws3 to ws5 $\div$ ws3                        |

| WFDIVR | wd16, wd18 | ; set wd16 to wd18 ÷ wd16                          |

| WFDIVR | ws2, EAX   | ; set ws2 to EAX $\div$ ws2                        |

| WFDIVR | ws7, Pl    | ; set ws2 to PI ÷ ws7                              |

| WFSQRT | ws3, ws5   | ; set ws3 to SQRT(ws5)                             |

| WFSQRT | wd10, wd12 | ; set wd10 to SQRT(wd12)                           |

|        |            |                                                    |

Figure 30. Examples of arithmetic instructions

#### COMPARE AND TEST INSTRUCTIONS

Compare and test instructions either compare two floating-point values or compare a single floating-point value to zero. The compare instructions compare Source1 to Source2. Besides comparing the operand to zero, as does the test operation (wftst), test with trap (wftstt) generates an invalid operation exception if the operand is not a valid number (Not a Number, NaN). Test instructions always operate on Source1. Compare and test instructions affect the condition code field of the process context register as shown in figure 27 on page 23.

#### SIGN MANIPULATION INSTRUCTIONS

The WTL 3167 has two functions that manipulate the sign of a floating-point number: negate and absolute value.

| WFCMPR<br>WFCMPRT | ws3, ws4<br>wd8, wd10 | ; perform reversed comparison<br>; perform reversed comparison and generate<br>; invalid exception if one (or both) of the operands is not a<br>; valid number |

|-------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WFTST<br>WFTSTT   | wd4<br>ws1            | ; perform the test of wd4<br>; perform the test of ws1 and generate                                                                                            |

|                   |                       | ; invalid exception if the operand is not a valid number                                                                                                       |

Figure 31. Examples of compare and test instructions

| WFNEG | ws1, ws1   | ; negate ws1                           |  |

|-------|------------|----------------------------------------|--|

| WFNEG | ws1, ws2   | ; set ws1 to -ws2                      |  |

| WFNEG | wd4, wd6   | ; set wd4 to -wd6                      |  |

| WFNEG | ws3, EAX   | ; set ws3 to -EAX                      |  |

| WFABS | ws3, ws4   | ; set ws3 to the absolute value of ws4 |  |

| WFABS | wd10, wd10 | ; coerce wd10 to its absolute value    |  |

|       |            |                                        |  |

Figure 32. Examples of sign manipulation instructions

#### PRELIMINARY DATA September 1988

### **Applications Programmer's Section, continued**

#### PROGRAMMING EXAMPLE

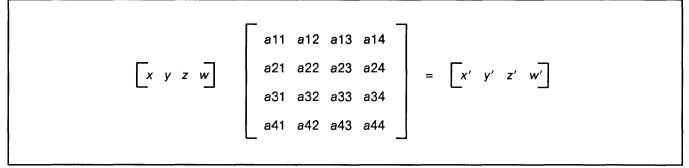

The following example shows the code for a  $4 \times 4$  matrix transformation written using the macros provided by WEITEK.

The variables x, y, z, and w are in memory locations X, Y, Z, and W. The variables x', y', z', and w' are stored back in memory location X, Y, Z, and W.

The matrix coefficients  $a_{11}$ , ...,  $a_{44}$  are assumed to be already stored in the WTL 3167 registers ws16-ws31.

Figure 33. Matrix multiplication

|   | MOV    | EAX, X    | ; load x into 386 EAX register                                                          |

|---|--------|-----------|-----------------------------------------------------------------------------------------|

|   | WFLD   | ws4, EAX  | ; load x into ws4                                                                       |

| ł | MOV    | EAX, Y    | ; load y into 386 EAX register                                                          |

|   | WFLD   | ws5, EAX  | ; load y into ws5                                                                       |

|   | MOV    | EAX, Z    | ; load z into 386 EAX register                                                          |

| ſ | WFLD   | ws6, EAX  | ; load z into ws6                                                                       |

|   | MOV    | EAX, W    | ; load w into 386 EAX register                                                          |

|   | WFLD   | ws7, EAX  | ; load w into ws7                                                                       |

|   | WFLD   | ws2, ws16 | ; move an into ws2                                                                      |

|   | WFMUL  | ws2, ws4  | ; ws2 = $a_{11} \times x$                                                               |

| l | WFMAC  | ws17, ws5 | ; ws2 = $(a_{11} \times x) + (a_{21} \times y)$                                         |

|   | WFMAC  | ws18, ws6 | ; ws2 = $(a_{11} \times x) + (a_{21} \times y) + (a_{31} \times z)$                     |

|   | WFMAC  | ws19, ws7 | ; ws2 = $(a_{11} \times x) + (a_{21} \times y) + (a_{31} \times z) + (a_{41} \times w)$ |

|   | WFST   | EAX, ws2  | ; store x'                                                                              |

|   | MOV    | X, EAX    | ; store x' into memory location X                                                       |

|   | WFLD   | ws2, ws20 | ; move a12 into R2                                                                      |

|   | WFMUL  | ws2, ws4  | ; ws2 = $a_{12} \times x$                                                               |

|   | WFMAC  | ws21, ws5 | ; ws2 = $(a_{12} \times x) + (a_{22} \times y)$                                         |

| ſ | WFMAC  | ws22, ws6 | ; ws2 = $(a_{12} \times x) + (a_{22} \times y) + (a_{32} \times z)$                     |

|   | WFMAC  | ws23, ws7 | ; ws2 = $(a_{12} \times x) + (a_{22} \times y) + (a_{32} \times z) + (a_{42} \times w)$ |

| l | WFST   | EAX, ws2  | ; store y'                                                                              |

|   | MOV    | Y, EAX    | ; store y' into memory location Y                                                       |

|   | WFLD   | ws2, ws24 | ; move a13 into ws2                                                                     |

| l | WFMUL. | ws2, ws4  | ; ws2 = a13 $\times x$                                                                  |

| ļ | WFMAC  | ws25, ws5 | ; ws2 = $(a_{13} \times x) + (a_{23} \times y)$                                         |

|   | WFMAC  | ws26, ws6 | ; ws2 = $(a_{13} \times x) + (a_{23} \times y) + (a_{33} \times z)$                     |

| ļ | WFMAC  | ws27, ws7 | ; ws2 = $(a_{13} \times x) + (a_{23} \times y) + (a_{33} \times z) + (a_{43} \times w)$ |

|   | WFST   | EAX, ws2  | ; store z'                                                                              |

| ł | MOV    | Z, EAX    | ; store z' into memory location Z                                                       |

|   | WFLD   | ws2, ws28 | ; move a14 into ws2                                                                     |

|   | WFMUL  | ws2, ws4  | ; ws2 = $a_{14} \times x$                                                               |

| ſ | WFMAC  | ws29, ws5 | ; ws2 = $(a_{14} \times x) + (a_{24} \times y)$                                         |

|   | WFMAC  | ws30, ws6 | ; ws2 = $(a_{14} \times x) + (a_{24} \times y) + (a_{34} \times z)$                     |

|   | WFMAC  | ws31, ws7 | ; ws2 = $(a_{14} \times x) + (a_{24} \times y) + (a_{34} \times z) + (a_{44} \times w)$ |

| l | WFST   | EAX, ws2  | ; store w'                                                                              |

|   | MOV    | W, EAX    | ; store w' into memory location W                                                       |

| 1 |        |           |                                                                                         |

| Figure 34. | Matrix | transformation | in | assembly | language |  |

|------------|--------|----------------|----|----------|----------|--|

|------------|--------|----------------|----|----------|----------|--|

#### PRELIMINARY DATA September 1988

### **Applications Programmer's Section, continued**

#### INSTRUCTION SUMMARY

Figure 35 summarizes the WTL 3167 instruction set macros. All WTL 3167 register names begin with "w". We follow the "w" with either "s" for single, "d" for double, or "x" meaning either "s" or "d". The register name ends with the letter "t" or "f". "t" stands for "to" and "f" stands for "from". For most instructions, wxt is the destination register and wxf is the source register.

|   | Data Move | ment              |                                                      |

|---|-----------|-------------------|------------------------------------------------------|

|   | WFLD      | wst, wsf          | ; load: wst = wsf                                    |

|   | WFLD      | wst, data         | ; load: wst = 386 data                               |